# **SERVICE MANUAL FOR**

BY: Meg.chen Technical Maintenance Department/GTK MTC Nov.2009/R00 Mitac 🍩

## Contents

| 1. Hardware Engineering Specification           | •• 3   |

|-------------------------------------------------|--------|

| 1.1 Introduction                                | 3      |

| 1.2 System Overview                             | • 4    |

| 1.3 Functions Description                       | · 14   |

| 1.4 Electrical Characteristic                   | · 22   |

| 1.5 Reference Documents                         | ·· 24  |

| 2. System View and Disassembly                  | •• 24  |

| 2.1 System View                                 | 26     |

| 2.2 Tools Introduction                          | · 28   |

| 2.3 System Disassembly                          | ·· 29  |

| 3. Definition & Location of Connectors/Switches | •• 45  |

| 3.1 Mother Board                                | ··· 45 |

|                                                 |        |

| 4. Pin Descriptions of Major Components         | •• 48  |

| 4.1 Cantiga North Bridge                        | . 48   |

| 4.2 ICH9M South Bridge                          | . 66   |

#### Contents

| System Block Diagram                           | •••• 108 |

|------------------------------------------------|----------|

| Trouble Shooting                               | 109      |

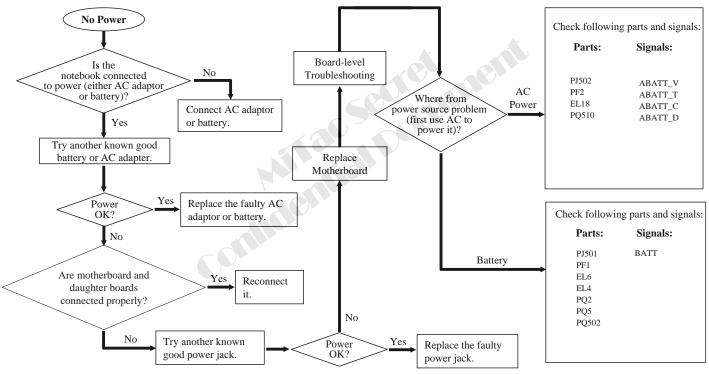

| 6.1 No Power                                   | 111      |

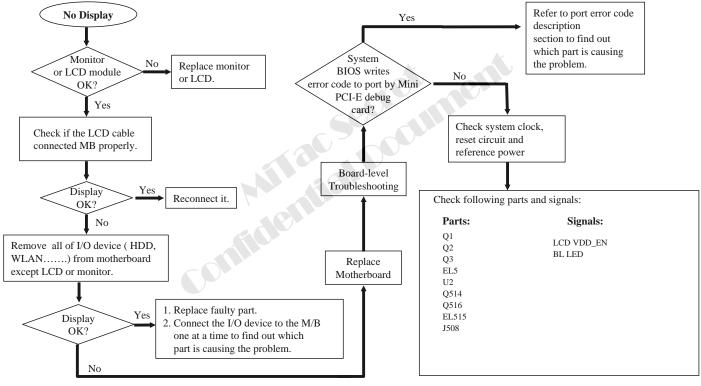

| 6.2 No Display                                 | 112      |

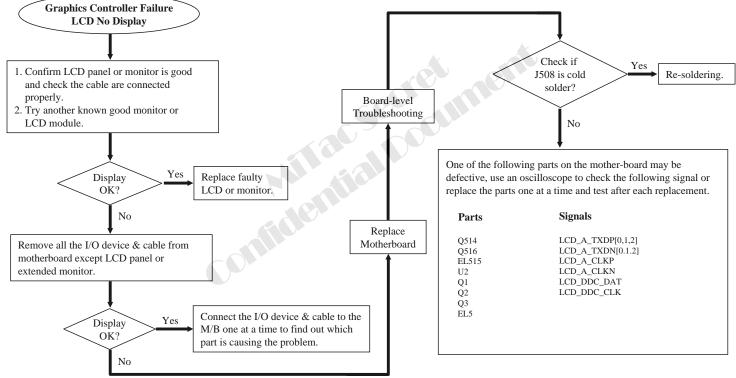

| 6.3 Graphics Controller Failure LCD No Display |          |

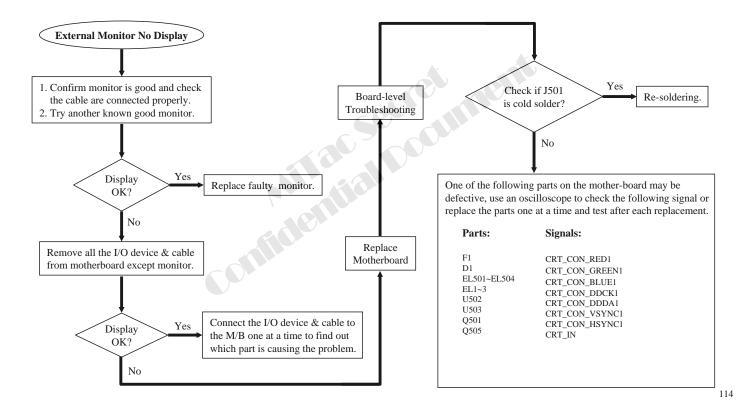

| 6.4 External Monitor No Display                | 114      |

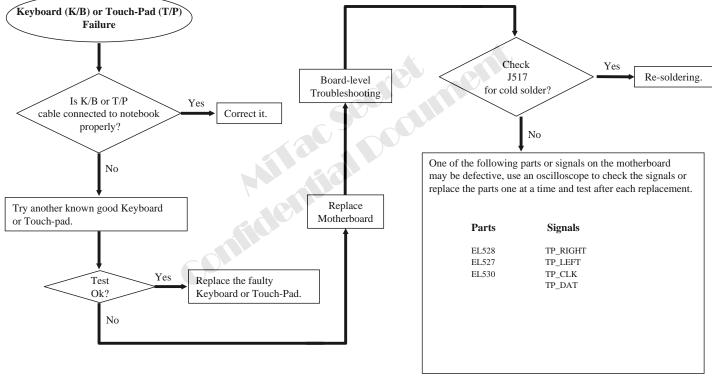

| 6.5 Keyboard (K/B) & Touch-Pad (T/P) Failure   |          |

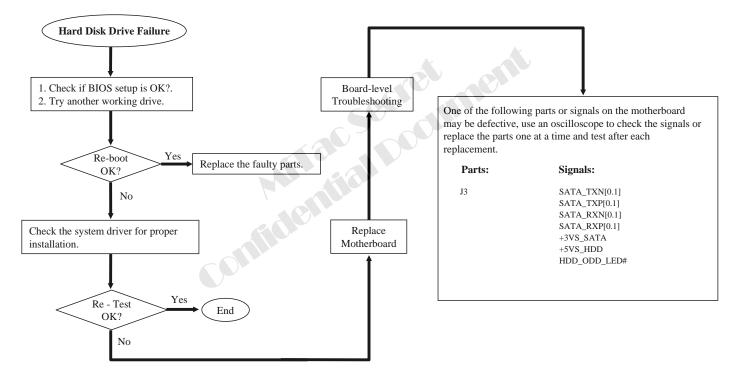

| 6.6 Hard Disk Driver Failure                   |          |

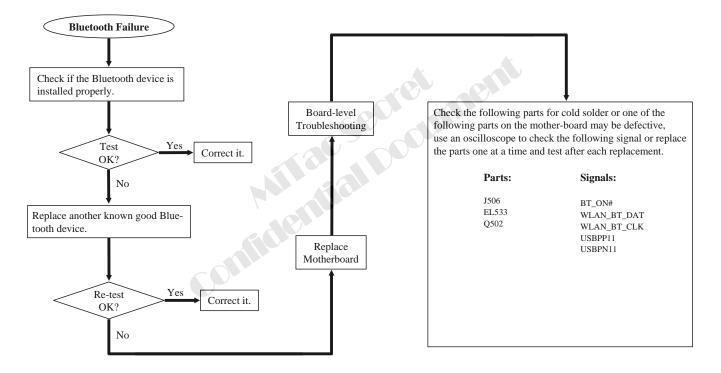

| 6.7 Bluetooth Failure                          |          |

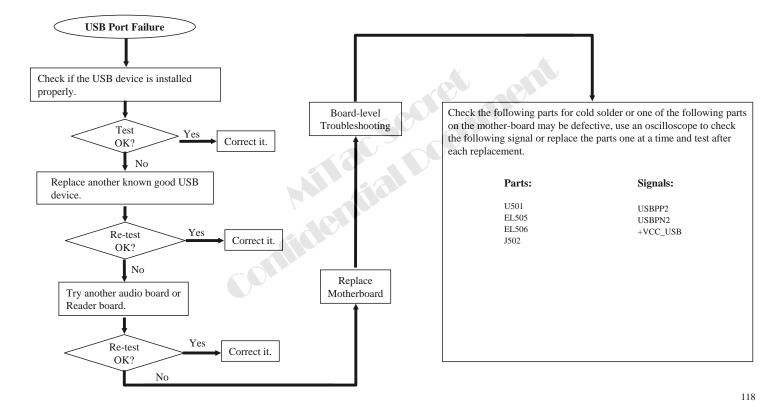

| 6.8 USB Port Failure                           |          |

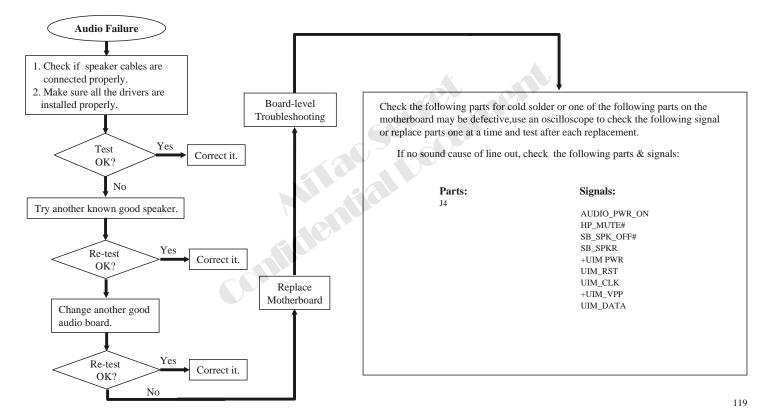

| 6.9 Audio Failure                              |          |

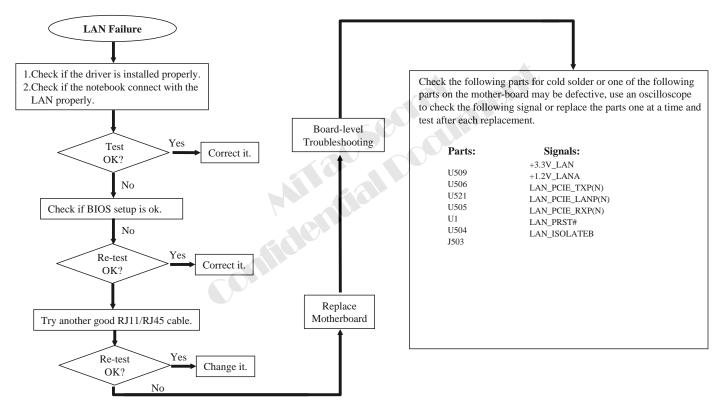

| 6.10 LAN Failure                               |          |

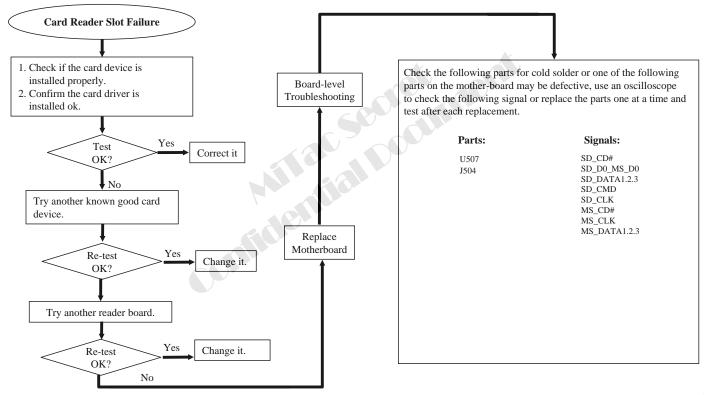

| 6.11 Card Reader slot Failure                  |          |

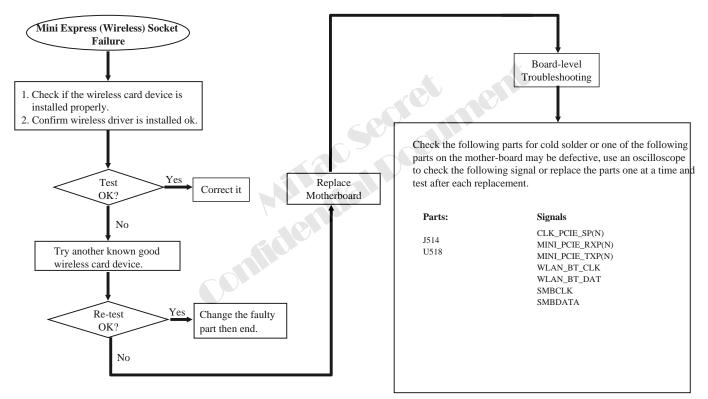

| 6.12 Mini Express (Wireless) Socket Failure    |          |

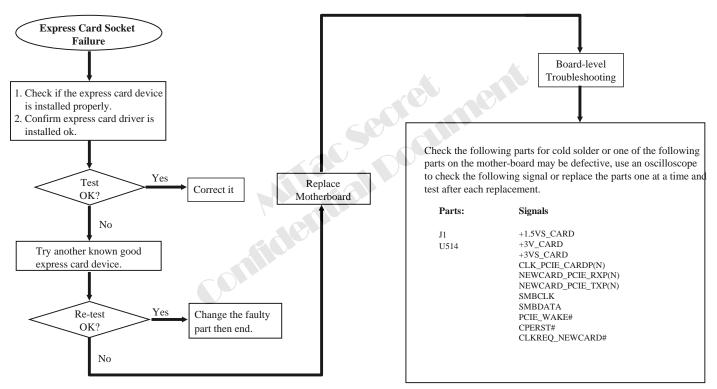

| 6.13 Express Card Socket Failure               | 123      |

## **1. Hardware Engineering Specification**

## **1.1 Introduction**

## **1.1.1 General Description**

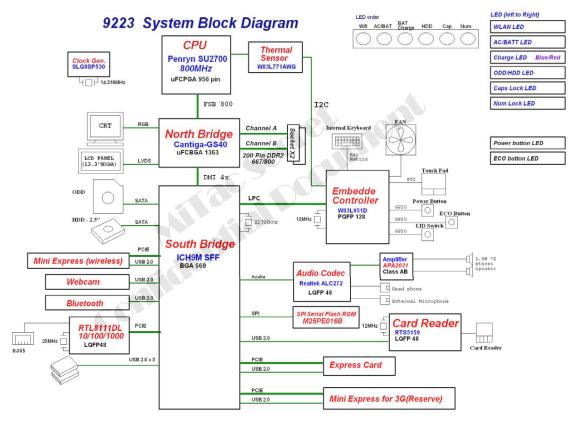

The 9223 motherboard is Intel Montevina SFF Platform with Mobile Penryn ULV on Intel's advance 45 nm process technology with copper interconnect. The processor provides a high-performance low-power mobile processor based on the Intel Mobile processor architecture.

9223 platform implements Intel Cantiga GS40 SFF / ICH9-M SFF core logic. The Intel Cantiga GS chipset-based Memory Controller Hub and the Intel I/O Controller Hub 9 Mobile SFF(ICH9-M).

The GMCH component provide the host interface controller, system memory interface (SDRAM) ,Direct Media interface ,Integrated Graphics engine. The ICH9-M integrate a number of I/O device controller and interface for legacy and high-speed device.

## **1.2 System Overview**

| Basic I | Function | Spec                                                                               | Remark                                         |

|---------|----------|------------------------------------------------------------------------------------|------------------------------------------------|

| CPU     |          |                                                                                    | CPU 10W                                        |

|         | Туре     | Mobile Penryn Montevina ULV CPU SU2700<br>Mobile Penryn Montevina Celeron CPU C723 | Montevina SFF SKU<br>FSB 800                   |

|         | TDP      | 10W TDP chassis design                                                             | Chipset NB low 7-8W,high 10-12.5W, SB 2.0-2.5W |

| Displa  | у        | -13.3 1366x768 LED w/z driver<br>-Max Brightness :TBD<br>EDID Support              |                                                |

| Chipse  | t        | Intel Cantiga GS40 + ICH9M-enhanced SFF                                            |                                                |

| Memor   | ry       |                                                                                    |                                                |

|         | Туре     | DDRII 667/800 1GB/2GB                                                              |                                                |

|         | Slot     | 2 SO-DIMM                                                                          |                                                |

|         | Max Size | 4GB                                                                                |                                                |

Continue to the previous page

| Graphi      | ic        | UMA                          |   |                               |

|-------------|-----------|------------------------------|---|-------------------------------|

| Audio       |           |                              |   |                               |

|             | Interface | Azalia                       |   | ALC 272                       |

|             | Speaker   | 1.5W speaker x2              | K | with Speaker Box              |

|             | Int. Mic  | 1 mic array                  |   | <b>N</b> OI                   |

|             | Volume    | S/W volume control by K/B    |   |                               |

|             | Quality   | TBD                          |   |                               |

|             | Buzzer    | Not Support                  |   |                               |

| Expres      | ss Card   |                              |   |                               |

|             | Slot Type | Express Card Type I 34 mm x1 |   | PCI-E & USB interface support |

|             | Function  | Hot plug V                   |   |                               |

| Card Reader |           | 3 in 1 (Realtek)             |   | USB interface                 |

|             | Slot Type | SD/MS/MS Pro/MMC             |   | 3 in 1 type                   |

|             |           |                              |   |                               |

| Comm | unication | Spec                    |   | Remark    |

|------|-----------|-------------------------|---|-----------|

| LAN  |           |                         |   |           |

|      | Conn. I/F | RJ45 Jack               |   | RTL8111DL |

|      | Slot Type | On board LAN solution   |   |           |

|      | Spec      | 10/100/1000 LAN (PCI-E) |   |           |

|      | Function  | Boot on LAN             | v |           |

|      |           | Wake on LAN in S3       | v |           |

|      |           | Wake on LAN in S4       | Х |           |

|      |           | Alert on LAN            | Х |           |

6

Continue to the previous page

Continue to the previous page

| Wirele | ess LAN         |                                                 |                                                                                                  |

|--------|-----------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------|

|        | Slot Type       | Mini PCI-E x2                                   |                                                                                                  |

|        | Antenna         | МІМО                                            | 1.3G (EU first) + MIMO + BT for antenna<br>(US 2 <sup>nd</sup> priority)<br>2.All Antenna on top |

|        | Module Spec     | 1.802.11 b/g/n , AW-NE771<br>2.3G , EM770       | МІМО                                                                                             |

|        | Others          | Radio wave enable by Fn+F1 key or killer Switch |                                                                                                  |

|        | Power on status | Remain the same status of last power off        |                                                                                                  |

7

\_\_\_\_\_

Downloaded from <u>www.Manualslib.com</u> manuals search engine

| Bluetooth |                 |                      | BTO if possible           |

|-----------|-----------------|----------------------|---------------------------|

|           |                 |                      |                           |

|           | Slot Type       | 8 pin                | Test criteria: 1Mbps @10m |

|           | Antenna         | Antenna on panel top |                           |

|           | Module Spec     | AW-BT252             |                           |

|           | Others          |                      |                           |

|           | Power on status |                      |                           |

| Webca     | ım              | BILL                 |                           |

|           | Slot Type       |                      |                           |

|           | Module Spec     | AuzreWave, AM-1B013  |                           |

|           | Interface       | USB/UVC function     |                           |

8

Continue to the previous page

Continue to the previous page

| Storage Device |                      | Spec             |                  | Remark               |

|----------------|----------------------|------------------|------------------|----------------------|

| HDD SATA       |                      | SATA I/F,2.5'' h | eight HDD        | 160/250/320 GB       |

| ODD            |                      | 9.5mm height Ol  | DD               | SATA interface       |

|                | Туре                 | Super Multi/DVI  | D-Dual/DVD COMBO | Digital support only |

|                | Structure            |                  |                  |                      |

|                |                      |                  |                  |                      |

| I/O In         | nterface             | Spec             | ×                | Remark               |

| Video          | output               | D-sub x 1        |                  | Vista                |

| USB            |                      | Port x3 (USB2.0  | 680              |                      |

| Audio          | o Jack               | HP Out           | ac - 000         | Black                |

|                |                      | Mic in           |                  | Black                |

| LAN            |                      | RJ45             |                  |                      |

|                |                      | FOL              |                  |                      |

| User           | Interface            | Spec             |                  | Remark               |

| Button /Switch |                      |                  |                  | One touch solution   |

|                | Power button         | Push button type |                  |                      |

|                | ECO Push button type |                  |                  |                      |

| Continue to the previous p | age                     |        |

|----------------------------|-------------------------|--------|

| Status LED                 |                         |        |

| WLAN                       | Blue                    |        |

| AC/BATT                    | Blue/Red                |        |

| Charge                     | Blue                    | ent    |

| HDD/ODD                    | Blue                    |        |

| Caps Lock                  | Blue                    |        |

| Num Lock                   | Blue                    |        |

| PWR button                 | Blue                    |        |

| ECO button                 | Blue                    |        |

| Input Device               | Spec                    | Remark |

| Keyboard                   |                         |        |

| Pitch/Stroke               | 19mm Pitch/1.7mm Stroke |        |

Continue to the previous page

| e to the previous | page            |             |      |                                             |

|-------------------|-----------------|-------------|------|---------------------------------------------|

| Dimension         | 300mm           |             |      |                                             |

| Function Key      |                 | OS          | Beep |                                             |

| Radio on/off      | Fn+F1 (WLAN)    | Windows     | TBD  |                                             |

| Radio on/off      | X               |             | TBD  | BUL                                         |

| Sound down        | Fn+F3           | Windows     | TBD  |                                             |

| Sound up          | Fn+F4           | Windows     | TBD  |                                             |

| Display Change    | Fn+F5           | Dos/Windows | TBD  | Behaviour:<br>LCD→LCD+CRT→CRT→LCD           |

| Brightness down   | Fn+F6 16 levels | Dos/Windows | TBD  | Switch to battery model still keep original |

| Brightness up     | Fn+F7 16 levels | Dos/Windows | TBD  | brightness level                            |

| T/P on/off        | x               |             | TBD  |                                             |

| Mute on/off       | Fn+F10          | Windows     | TBD  | Mute system master volume                   |

| Panel on/off      | Fn+F11          | Dos/Windows | TBD  | Backlight Off                               |

| Suspend           | Fn+F12          | Windows     | TBD  |                                             |

|                   |                 |             |      |                                             |

Continue to the previous page

| Pointing Device  | Synaptics: TM391                                             | Under plastic        |

|------------------|--------------------------------------------------------------|----------------------|

| Function         | Glide pad with 2 buttons                                     |                      |

| Pin              | 12 Pin                                                       |                      |

|                  |                                                              |                      |

| Power            | Spec                                                         | Remark               |

| Battery          | SBO I                                                        | Gauge IC 20Z90       |

| Туре             | Li-ion type                                                  |                      |

| Capacity         | 2250mAh                                                      |                      |

| Cells No.        | 6 cells                                                      |                      |

| Battery Life     | Target:<br>4.5 hours with backlight min. with 6 cell battery | ECO mode             |

| Power off Charge | Target:2 hrs to 90%(6 cells )                                |                      |

| Power on Charge  | Target: TBD                                                  | Idle mode            |

| S3 Suspend Time  | Target: TBD                                                  |                      |

| RTC Battery      | Not chargeable                                               | 5 years battery life |

Continue to the previous page

| AC   | Adapter      | 65W 3 pin DC                                                        |      |

|------|--------------|---------------------------------------------------------------------|------|

|      | Input        | AC 100-240V                                                         |      |

|      | Vendor       | Delta                                                               | BILL |

| Leal | kage Current | Battery remain 20% after 30 Days w/z 100% battery capacity (6 cell) | TBD  |

|      |              |                                                                     |      |

## **1.3 Function Description**

## 1.3.1 CPU

- The Penryn Processor SU2700 on 45-nanometer process technology (also referred to as CPU and processor in this document) with the following new features:

- 800-MTs Source-Synchronous Front Side Bus (FSB)

- Intel® Trusted Execution Technology (Intel® TxT)

- SSE4.1 instructions

• New Deep Power Down Technology (also called C6 state) low power state which further reduces power consumption when the processor is idle

• Enlarged 2-MB L2 cache memory

#### **1.3.2 CORE LOGIC**

#### Cantiga

- The Cantiga chipset Graphics Memory Controller Hub (also referred to as the (G)MCH in the document) and ICH9M I/O controller hub with the following new features.

- Gen 5.0 Integrated Graphics Engine

- 400-MHz core render clock at 1.05-V core voltage

- Support for DDR2 at 800 and 667 MTs

- ICH9-M

• The ICH9M I/O controller hub (also referred to as ICH9M in the document) is a follow-on product to Intel ICH8M with the following enhancements.

- 12 USB ports

- 4 SATA ports

- Support for Intel® Active Management Technology (Intel® AMT) 4.0

- Support for Integrated Trusted Port module 1.2

- CPU Deep Power Down Technology (also called C6 state) state support

## **1.3.3 Memory**

Support DDR2 667/800 MHz SO-DIMM expandable to 4GB (2 DDR2-SODIMM slots)

| Slot1 | Slot2 | Total |  |  |  |

|-------|-------|-------|--|--|--|

| 1GB   | 0GB   | 1GB   |  |  |  |

| 2GB   | 0GB   | 2GB   |  |  |  |

| 1GB   | 1GB   | 2GB   |  |  |  |

| 2GB   | -2GB  | 4GB   |  |  |  |

|       |       |       |  |  |  |

## **1.3.4 I/O PORTS**

- CRT Port

- Standard VGA compatible port

- DDC1 and DDC2B compliant

| PIN | SIGNAL        | DESCRIPTION               |

|-----|---------------|---------------------------|

| 1   | CRT_RED       | Red analog video output   |

| 2   | CRT_GREEN     | Green analog video output |

| 3   | CRT_BLUE      | Blue analog video output  |

| 4   | Monitor Sense | NC                        |

| 5   | GND           | Monitor Sense             |

| 6   | GND           | Ground                    |

| 7   | GND           | Ground                    |

| 8   | GND           | Ground                    |

| 9   | VCC           | +5VDC                     |

| 10  | GND           | Ground                    |

| 11  | Monitor Sense | NC                        |

| 12  | CRT_DDDA      | Data from DDC monitor     |

| 13  | CRT_HSYNC     | Horizontal Sync control   |

| 14  | CRT_VSYNC     | Vertical Sync control     |

| 15  | CRT_DDCK      | Clock to DDC monitor      |

|     | nfi Ole       | ·                         |

#### ✤ RJ-45

- RTL8111DL Integrated 10/100/1000 transveiver

- Supports PCI ExpressTM 1.1

- •Auto-Negotiation with Next Page capability

• The Fast Ethernet MAC Controller features an IEEE802.3 and IEEE802.3x compliant MAC with external LAN physical layer chip supporting full duplex control.

• Support Wake-up On-LAN function from S3.

| Pin | Signal Name       | Direction | Description                   |

|-----|-------------------|-----------|-------------------------------|

| 1   | PJTX+             | Out       | Transmit Data Ring            |

| 2   | PJTX-             | Out       | Transmit Data Tip             |

| 3   | PJRX+             | IN        | Receive Data Ring             |

| 4   | PJRX-             | IN        | Receive Data Tip.             |

| 5   | MDO2+ / RJ45_PJ4  |           | Internal termination resistor |

| 6   | MDO2- / RJ45_PJ4  | - C       | Internal termination resistor |

| 7   | MDO3 + / RJ45_PJ7 | -         | Internal termination resistor |

| 8   | MDO3 - / RJ45_PJ7 | -         | Internal termination resistor |

|     |                   |           |                               |

USB Ports

• Four industry standard USB 2.0 ports (Backward compatible to USB 1.1)

• Support maximum transfer rate up to 480Mbits/s

| Pin | Signal Name | Direction | Description              |

|-----|-------------|-----------|--------------------------|

| 1   | VCC         | Power     | USB Device Power (+5VDC) |

| 2   | DATA-       | I/O       | Balanced Data Negative   |

| 3   | DATA+       | I/O       | Balanced Data Positive   |

| 4   | GND         | Ground    | Ground                   |

- Card Reader Port

- Support SD, MMC, Memory Stick, Memory Stick Duo (adapter), Memory Stick Pro.

- 3 in1 combo connector

#### **1.3.5 DISPLAY**

- 13.3" WXGA(1366x768 pixels) display size for notebook PC

- •• LED Backlight with LED controller IC

- Glare Surface ••

- Bezel less structure

# I Flach 1.3.6 READ ONLY MEMORY (SPI Serial Flash)

- \* Fully compatible with industry standard software including Windows Vista.

- Fully supports APM V1.2 and latest ACPI specification

- 1Mx8 (8Mbit) SPI Serial Flash BIOS

- Phoenix BIOS core (EFI)

## **1.3.7 POWER MANAGEMENT FEATURES**

Local standby mode (Individual devices such as HDD, graphics controller, LCD etc..)

- CPU Idle mode (Including ACPI modes C0, C1, C2, C3,C4 and C6)

- Suspend mode (S3 & S4 ACPI modes)

- ✤ Fully APM-base legacy power.

- Fully ACPI V1.0b, 2.0 and 3.0, compliant.

- ✤ Hibernate for Vista.

- Thermal management.

# 1.3.8 KEYBOARD CONTROLLER

Winbond W83L951D.

#### **1.3.9 LEDs INDIACTOR**

WiFi & AC/BAT & Charger & CDROM +HDD & Cap lock & Num lock.

## **1.3.10 TOUCH PAD MODULE**

Synaptics TM61P-391

## **1.4 Electrical Characteristic**

## 1.4.1 Power Consumption Of Suspend Mode

♦ Suspend To RAM < 50mA

Suspend To Disk / Soft-Off /Mechanical Off < 1mA</p>

| Pow  | er           | Spec                                                        | Remark         |

|------|--------------|-------------------------------------------------------------|----------------|

| Batt | ery          |                                                             | Gauge IC 20Z90 |

|      | Туре         | Li-ion type                                                 |                |

|      | Capacity     | 2250mAh (P) (S)                                             |                |

|      | Cells No.    | 6 cells                                                     |                |

|      | Battery Life | Target:<br>4.5 hours with backlight min. w/z 6 cell battery | ECO mode       |

|     | Power off Charge | Target:2 hrs to 90%(6 cells )                                       |                      |

|-----|------------------|---------------------------------------------------------------------|----------------------|

|     | Power on Charge  | Target: TBD                                                         | Idle mode            |

|     | S3 Suspend Time  | Target: TBD                                                         |                      |

|     | RTC Battery      | Not chargeable                                                      | 5 years battery life |

| AC  | Adapter          | 65W 3 pin DC                                                        |                      |

|     | Input            | AC 100-240V                                                         |                      |

|     | Vendor           | Delta                                                               |                      |

| Pow | ver Consumption  | Battery remain 20% after 30 Days w/z 100% battery capacity (6 cell) | TBD                  |

|     |                  |                                                                     |                      |

## **1.5 Reference Documents**

| Documents                                                                                          | Revision |

|----------------------------------------------------------------------------------------------------|----------|

| Montevina Platform Design Guide for Penryn Processor, Cantiga Chipset and ICH9M I/O Controller Hub | 2.1      |

| Penryn Processor for Montevina Platform                                                            | 2.2      |

| Cantiga Chipset External Design Specification (EDS)                                                | 2.4      |

| Intel® I/O Controller Hub 9 (ICH9) Family External Design Specification (EDS) – Volume 1           | 2.3      |

| Realtek ALC272                                                                                     | 0.9      |

| Realtek RTS5159 USB 2.0 Card Reader Controller                                                     | 0.93     |

| PC2001 System Design Guide                                                                         | 0.7      |

| PCI Local Bus Specification                                                                        | 2.2      |

| SILEGO SLG8SP552                                                                                   | 0.1      |

| TUEL                                                                                               |          |

|                                                                                                    |          |

## Appendix B Function Key Definition

| Function Key    |                   |                                                |

|-----------------|-------------------|------------------------------------------------|

| Radio on/off    | Fn+F1 (WLAN)      | w/o bibi sound                                 |

| Radio on/off    | Fn+F1 (Bluetooth) | TBD                                            |

| Sound down      | Fn+F3             | w/o bibi sound                                 |

| Sound up        | Fn+F4             | w/o bibi sound                                 |

| Display Change  | Fn+F5             | W/o bibi sound                                 |

| Brightness down | Fn+F6 8 levels    | w/o bibi sound<br>Could control it in DOS mode |

| Brightness up   | Fn+F7 8 levels    |                                                |

| Mute on/off     | Fn+F10            | Mute system master volume                      |

| Panel on/off    | Fn+F11            | Disable backlight                              |

|                 |                   | w/o bibi sound                                 |

| Suspend         | Fn+F12            | w/o bibi sound                                 |

| Power low       |                   | w/z bibi sound                                 |

## 2. System View and Disassembly

## 2.1 System View

#### 2.1.2 Left-side View

- Power Connector

- **2** VGA Port

- USB Port

- RJ-45 Connector

- G Card Reader

- Express card slot

## 2.1.2 Right-side View

- Super Multi Drive

- Audio output Connector

- Microphone Connector

- **4** USB Port

- **6** Kensington Lock

| Sector   | 0 9 | <br>G<br>G  |

|----------|-----|-------------|

| or<br>or |     | <br>2 6 9 6 |

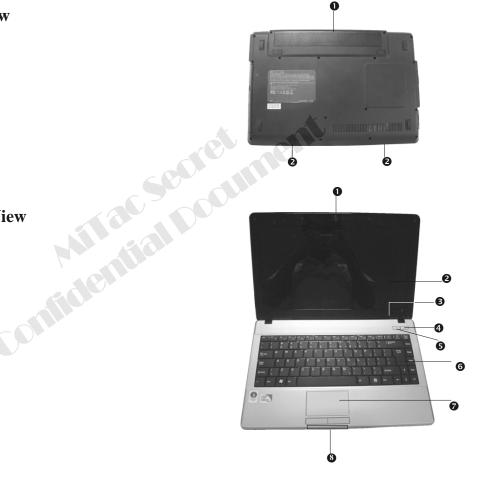

## 2.1.3 Bottom View

- Battery Pack

- Stereo Speaker

## 2.1.4 Top-open View

- Camera

- **2** LCD Screen

- Microphone

- Power Button

- G ECO Button

- Keyboard

- Touch Pad

- Indicators

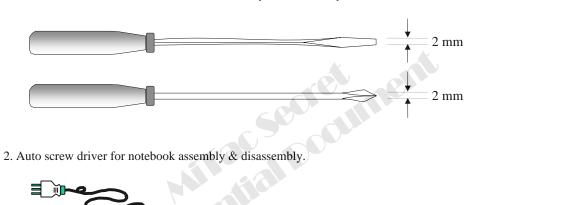

## **2.2 Tools Introduction**

1. M2.0

1. Screw driver with bit size for notebook assembly & disassembly.

|            |         |      |          | #0 |

|------------|---------|------|----------|----|

| Screw Size | Tooling | Tor. | Bit Size |    |

Auto Screwdriver

2.0-2.5 kg/cm2

#0

28

**Bit Size**

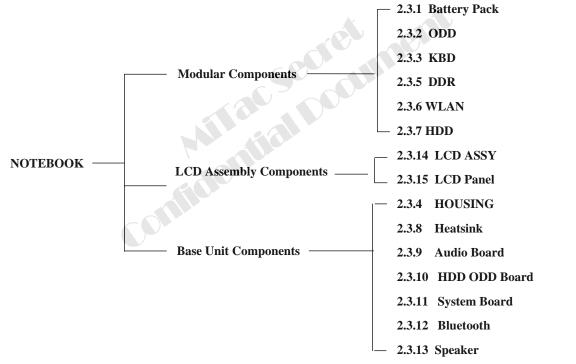

## 2.3 System Disassembly

The section discusses at length each major component for disassembly/reassembly and show corresponding illustrations. Use the chart below to determine the disassembly sequence for removing components from the notebook.

**NOTE:** Before you start to install/replace these modules, disconnect all peripheral devices and make sure the notebook is not turned on or connected to AC power.

#### 2.3.1 Battery Pack

#### Disassembly

- 1. Carefully put the notebook upside down.

- 2. Slide two release levers outwards to the "unlock" ( ☐ ) position ( **0**), while take the battery pack out of the compartment ( **2**). (Figure 2-1)

- 1. Replace the battery pack into the compartment. The battery pack should be correctly connected when you hear a clicking sound.

- 2. Slide the release lever to the "lock" ( $\square$ ) position.

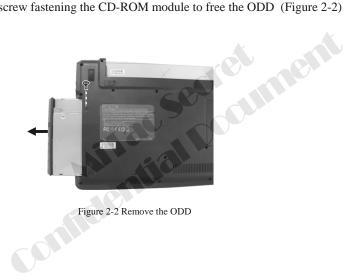

#### 2.3.2 ODD

#### Disassembly

- 1. Remove the battery pack. (Refer to section 2.3.1 Disassembly)

- 2. Remove one screw fastening the CD-ROM module to free the ODD (Figure 2-2)

- 1. Replace the ODD module, then secure with one screw.

- 2. Reassemble the battery pack. (See section 2.3.1 Reassembly)

#### 2.3.3 KBD

#### Disassembly

1. Remove the battery pack. (See section 2.3.1 Disassembly)

- 2. Loosen the six latches locking the keyboard. (Figure 2-3)

- 3. Slightly lift up the keyboard and disconnect the cable from the mother board, then separate the keyboard (Figure 2-4)

Figure 2-3 Loosen the six latches

Figure 2-4 Disconnect the cable

- 1. Reconnect the keyboard cable and fit the keyboard back into place with six latches.

- 2. Replace the battery pack. (See section 2.3.1 Reassembly)

#### 2.3.4 Housing

#### Disassembly

- 1. Remove the battery pack, ODD. (See section 2.3.1~2.3.2 Disassembly)

- 2. Remove sixteen screws and two Dummy card to free the housing. (Figure 2-5~2-6)

- 1. Replace the housing and secure with sixteen screws and dummy card.

- 2. Replace the battery pack, ODD. (See section 2.3.1~2.3.2 Reassembly)

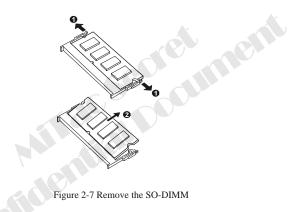

#### 2.3.5 DDR

#### Disassembly

- 1. Remove the battery pack, ODD, Housing. (See section 2.3.1~2.3.2, 2.3.4 Disassembly)

- 2. Pull the retaining clips outwards (**0**) and remove the SO-DIMM (**2**). (Figure 2-7)

- 1. To install the DDR2, match the DDR2's notched part with the socket's projected part and firmly insert the SO-DIMM into the socket at 20-degree angle. Then push down until the retaining clips lock the DDR2 into position.

- 3. Replace the battery pack, ODD, Housing. (See section 2.3.1~2.3.2, 2.3.4 Disassembly)

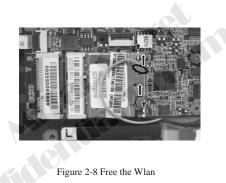

#### 2.3.6 Wlan

#### Disassembly

- 1. Remove the battery pack, ODD, Housing. (Refer to section 2.3.1~2.3.2, 2.3.4 Disassembly)

- 2. Disconnect the two antennae first, then remove two screws to free the wlan. (Figure 2-8)

- 1. Replace the wlan and secure with two screws.

- 2. Reconnect two antennae into wlan.

- 3. Replace the battery pack, ODD, Housing. (Refer to section 2.3.1~2.3.2, 2.3.4 Reassembly)

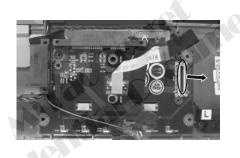

### 2.3.7 HDD

### Disassembly

- 1. Remove the battery pack, ODD, Housing, WLAN. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.6 Disassembly)

- 2. Remove the one screw and slide the HDD module out of the compartment. (Figure 2-9)

- 1. Slide the HDD module into the compartment and secure with one screw.

- 2. Replace the battery pack. ODD, Housing. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.6 Reassembly)

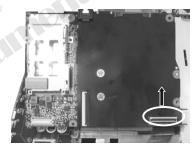

### 2.3.8 Heatsink

### Disassembly

- 1. Remove the battery pack, ODD, Housing, WLAN, HDD. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.7 Disassembly)

- 2. Remove five screws that secure with heatsink and disconnect the cable from system board. (Figure 2-10)

- 1. Replace the heatsink and secure with five screws.

- 2. Reconnect the cable from system board.

- 3. Replace the battery pack., ODD, Housing, WLAN, HDD. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.7 Reassembly)

### 2.3.9 Audio BD

### Disassembly

- 1. Remove the battery pack, ODD, Housing, WLAN, HDD, Heatsink. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.8 Disassembly)

- 2. Disconnect the three cables from audio board then remove one screw that secure with audio Board. (Figure 2-11)

Figure 2-11 Remove audio board

- 1. Replace the audio board and secure with one screw.

- 2. Reconnect the three cables to system board.

- 3. Replace the battery pack., ODD, Housing, WLAN, HDD, Heatsink. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.8 Reassembly)

### 2.3.10 HDD ODD Board

### Disassembly

- 1. Remove the battery pack, ODD, Housing, WLAN, HDD, Heatsink, Audio board. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.9 Disassembly)

- 2. Disconnect the cable from system board then pick up the HDD ODD board. (Figure 2-12)

Figure 2-12 Remove HDD ODD board

- 1. Replace the HDD ODD board and reconnect the cable to system board.

- 2. Replace the battery pack, ODD, Housing, WLAN, HDD, Heatsink, Audio board. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.9 Reassembly)

### 2.3.11 System Board

### Disassembly

- 1. Remove the battery pack, ODD, Housing, WLAN, HDD, Heatsink, Audio board, HDD ODD board. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.10 Disassembly)

- 2. Disconnect the three cables and remove threes screws from system board. (Figure 2-13)

- 3. Disconnect the cable from the back of the system board. (Figure 2-14)

Figure 2-13 Remove three screws and three cables

Figure 2-14 Remove System board

### Reassembly

1.Reconnect the cable from the back of the system board.

2.Replace the system board and secure with three screws and reconnect the cable from system board. 3.Replace the battery pack., ODD, Housing, WLAN, HDD, Heatsink, Audio board, HDD ODD board. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.10 Reassembly)

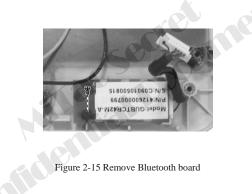

### 2.3.12 Bluetooth

### Disassembly

- 1. Remove the battery pack, ODD, Housing, WLAN, HDD, Heatsink, Audio board, HDD ODD board, System board. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.11 Disassembly)

- 2. Remove one screw to free the Bluetooth board. (Figure 2-15)

### Reassembly

- 1.To install the Bluetooth and secure with one screw .

- 2. Replace the battery pack., ODD, Housing, WLAN, HDD, Heatsink, Audio board, HDD ODD board, System board. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.11 Reassembly)

### 2.3.13 Speaker

### Disassembly

- 1. Remove the battery pack, ODD, Housing, WLAN, HDD, Heatsink, Audio board, HDD ODD board, System board, Bluetooth. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.12 Disassembly)

- 2. Remove four screws to free the speaker. (Figure 2-16)

Figure 2-16 Remove speaker

- 1.To install the speaker and secure with four screws .

- 2. Replace the battery pack., ODD, Housing, WLAN, HDD, Heatsink, Audio board, HDD ODD board, System board, Bluetooth. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.12 Reassembly)

### 2.3.14 LCD ASSY

### Disassembly

- 1. Remove the battery pack, ODD, Housing, WLAN, HDD, Heatsink, Audio board, HDD ODD board, System board, Bluetooth, Speaker. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.13 Disassembly)

- 2. Remove two screws to free the LCD ASSY. (Figure 2-17)

Figure 2-17 Remove two screws

- 1. Replace the LCD assembly and secure with two screws.

- 2. Replace the battery pack., ODD, Housing, WLAN, HDD, Heatsink, Audio board, HDD ODD board, System board, Bluetooth, Speaker. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.13 Reassembly)

### 2.3.15 LCD Panel

### Disassembly

- 1. Remove the battery pack, ODD, Housing, WLAN, HDD, Heatsink, Audio board, HDD ODD board, System board, Bluetooth, Speaker, lcd assy. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.14 Disassembly)

- 2. Remove two screws fastening the LCD cover. (Figure 2-18)

- 3. Remove two caps, Then remove two screws fastening the LCD cover. (Figure 2-19)

- 4. Insert a flat screwdriver to the lower part of the LCD cover and gently pry the frame out. Repeat the process until the cover is completely separated from the housing.

- 5. Carefully lift up the panel from the LCD housing.

Figure 2-18 Remove two screws

Figure 2-19 Remove hinges

6. Remove four screws fastening the LCD panel. (Figure 2-20)

7. Disconnect the cable to free the LCD panel. (Figure 2-21)

- 1. Replace the cable to the LCD, then replace LCD panel into the LCD housing and secure with four screws .

- 2. Replace the LCD cover and secure with four screws, then replace the two caps.

- 3. Replace the battery pack., ODD, Housing, WLAN, HDD, Heatsink, Audio board, HDD ODD board, System board, Bluetooth, Speaker, LCD assy. (Refer to section 2.3.1~2.3.2, 2.3.4~2.3.13 Reassembly)

## **3. Definition & Location of Major Components**

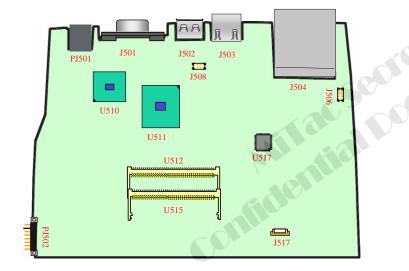

### 3.1 Mother Board (Side A)

- > PJ501 : Power Connector

- > J501 : VGA Connector

- J502 : USB Connector

- J503 : RJ45 Connector

- > J504 : Card Reader Connector

- PJ502 : Battery Connector

- > U510 : CPU

- > U511 : Cantiga-GS40 North Bridge

- J508 : LCD Connector

- J506 : Bluetooth Connector

- J517 : Touch Pad Connector

- > J512,J515 : DDR2 SO-DIMM Socket

- > U517 : System Bios

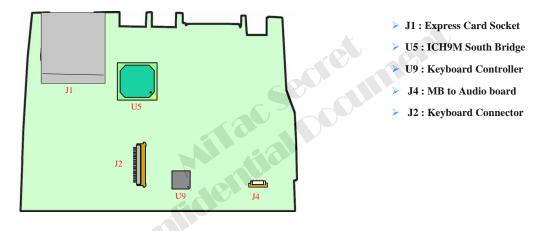

# 3. Definition & Location of Major Components

### 3.1 Mother Board (Side B)

## 4. Pin Descriptions of Major Components

## 4.1 Cantiga North Bridge -1

| Signal Name   | Туре      | Description                                                    |

|---------------|-----------|----------------------------------------------------------------|

| H_A#[35:3]    | I/O       | Host Address Bus: HA#[35:3] connects to the processor          |

|               | AGTL+2X   | address bus. During processor cycles the HA#[35:3] are         |

|               |           | inputs. The (G)MCH drives HA#[35:3] during snoop cycles on     |

|               |           | behalf of PCI Express/Internal Graphics or ICH. HA#[35:3]      |

|               |           | are transferred at 2x rate.                                    |

|               |           | Note that the address is inverted on the processor bus.        |

| H_ADS#        | I/O       | Host Address Strobe: The system bus owner asserts              |

|               | AGTL+     | H_ADS# to indicate the first of two cycles of a request phase. |

|               |           | The (G)MCH can also assert this signal for snoop cycles and    |

|               |           | interrupt messages.                                            |

| H_ADSTB#[1:0] | I/O       | Host Address Strobe: HA#[31:3] connects to the processor       |

|               | AGTL+2X   | address bus. During processor cycles, the source synchronous   |

|               |           | strobes are used to transfer HA#[35:3] and HREQ#[4:0] at       |

|               |           | the 2x transfer rate.                                          |

|               |           | Strobe Address Bits                                            |

|               |           | HADSTB#0 HA#[15:3], HREQ#[4:0]                                 |

|               |           | HADSTB#1 HA#[35:16]                                            |

|               |           |                                                                |

| H_AVREF       | I         | Host Reference Voltage: Reference voltage input for the        |

| H_DVREF       | A         | Data, Address, and Common clock signals of the Host AGTL+      |

|               | -         | interface                                                      |

| H_BNR#        | I/O AGTL+ | Host Block Next Request: Used to block the current             |

|               |           | request bus owner from issuing a new request. This signal is   |

|               |           | used to dynamically control the processor bus pipeline depth.  |

| H_BPRI#       | 0         | Host Bus Priority Request: The (G)MCH is the only Priority     |

|               | AGTL+     | Agent on the system bus. It asserts this signal to get the     |

|               |           | ownership of the address bus. This signal has priority over    |

|               |           | symmetric bus requests and will cause the current symmetric    |

|               |           | owner to stop issuing new transactions unless the H_LOCK#      |

|               |           | signal was asserted.                                           |

## 4.1 Cantiga North Bridge -2

| H_BREQ#   | I/O<br>AGTL+ | Host Bus Request: The (G)MCH pulls the processor bus<br>H_BREQ# signal low during H_CPURST#. The signal is<br>ampled by the processor on the active-to-inactive transition<br>of H_CPURST#. H_BREQ# should be tri-stated after the hold tir<br>requirement has been satisfied. |

|-----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H_CPURST# | O<br>AGTL+   | Host CPU Reset: The H_CPURST# pin is an output from the (G)MCH. The (G)MCH asserts H_CPURST# while RSTIN# is asserted and for approximately 1 ms after RSTIN# is deasserted. H_CPURST# allows the processor to begin execution in a known state.                               |

### Host Interface Signals(continued)

| Signal Name | Туре     | Description                                                          |

|-------------|----------|----------------------------------------------------------------------|

| H_CPUSLP#   | 0        | Host CPU Sleep: When asserted in the Stop-Grant state,               |

|             | LVCMOS   | causes the processor to enter the Sleep state. During Sleep          |

|             |          | state, the processor stops providing internal clock signals to       |

|             |          | all units, leaving only the Phase-Locked Loop (PLL) still operating. |

|             |          | Processors in this state will not recognize snoops or                |

|             |          | interrupts. (This is a CMOS type buffer with Vtt - NOT 3.3 volts.)   |

| H_D#[63:0]  | I/O      | Host Data: These signals are connected to the processor              |

|             | AGTL+ 4X | data bus. HD[63:0]# are transferred at 4x rate.                      |

|             |          | Note that the data signals are inverted on the processor bus         |

|             |          | depending on the HDINV#[3:0] signals.                                |

| H_DBSY#     | I/O      | Host Data Bus Busy: Used by the data bus owner to hold               |

|             | AGTL+    | the data bus for transfers requiring more than one cycle.            |

| H_DEFER#    | 0        | Host Defer: Signals that the (G)MCH will terminate the               |

|             | AGTL+    | transaction currently being snooped with either a deferred           |

|             |          | response or with a retry response.                                   |

# 4.1 Cantiga North Bridge -3

| H_DINV#[3:0]  | I/O     | Host Dynamic Bus Inversion: Driven along with the              |  |  |

|---------------|---------|----------------------------------------------------------------|--|--|

|               | AGTL+   | HD[63:0]# signals. Indicates if the associated signals are     |  |  |

|               | mon     | inverted or not. HDINV[3:0]# are asserted such that the        |  |  |

|               |         | number of data bits driven electrically low (low voltage)      |  |  |

|               |         | within the corresponding 16-bit group never exceeds 8.         |  |  |

|               |         |                                                                |  |  |

|               |         | H_DINV# Data Bits                                              |  |  |

|               |         | H_DINV#3 H_D#[63:48]                                           |  |  |

|               |         | H_DINV#2 H_D#[47:32]                                           |  |  |

|               |         | H_DINV#1 H_D#[31:16]                                           |  |  |

|               |         | H_DINV#0 H_D#[15:0]                                            |  |  |

|               |         |                                                                |  |  |

| H_DPWR#       | I/O     | Host Data Power: Used by (G)MCH to indicate that a data        |  |  |

|               | AGTL+   | return cycle is pending within 2 H_CLK cycles or more.         |  |  |

|               |         | Processor uses this signal during a read-cycle to activate the |  |  |

|               |         | data input buffers in preparation for H_DRDY#                  |  |  |

|               |         | and the related data.                                          |  |  |

| H_DRDY#       | I/O     | Host Data Ready: Asserted for each cycle that data is          |  |  |

|               | AGTL+   | transferred.                                                   |  |  |

| H_DSTBP#[3:0] | I/O     | Host Differential Host Data Strobes: The differential          |  |  |

| H_DSTBN#[3:0] | AGTL+4X | source synchronous strobes are used to transfer HD[63:0]#      |  |  |

|               |         | and HDINV#[3:0] at the 4x transfer rate.                       |  |  |

|               |         | Strobe Data Bits                                               |  |  |

|               |         | H_DSTBP#3, H_DSTBN#3 H_D#[63:48], H_DINV#[3]                   |  |  |

|               |         | H_DSTBP#2, H_DSTBN#2 H_D#[47:32], H_DINV#[2]                   |  |  |

|               |         | H_DSTBP#1, H_DSTBN#1 H_D#[31:16], H_DINV#[1]                   |  |  |

|               |         | H_DSTBP#0, H_DSTBN#9 H_D#[15:0], H_DINV#[0]                    |  |  |

|               |         |                                                                |  |  |

# 4.1 Cantiga North Bridge -4

| Host Interface S | ignals(continu | ed)                                                  |                                                    |

|------------------|----------------|------------------------------------------------------|----------------------------------------------------|

| Signal Name      | Туре           |                                                      | Description                                        |

| H_HIT#           | I/O            | Host Hit: Indicate                                   | es that a caching agent holds an unmodified        |

|                  | AGTL+          | version of the red                                   | quested line.                                      |

|                  |                | Also, driven in c                                    | onjunction with H_HITM# by the target to           |

|                  |                | extend the snoop                                     | window.                                            |

| H_HITM#          | I/O            | Host Hit Modifie                                     | d: Indicates that a caching agent holds a          |

|                  | AGTL+          | modified version                                     | of the requested line and that this agent          |

|                  |                | assumes respons                                      | ibility for providing the line.                    |

|                  |                | Also, driven in c                                    | onjunction with H_HIT# to extend the snoop window. |

| H_LOCK#          | Ι              | Host Lock: All pi                                    | ocessor bus cycles sampled with the                |

|                  | AGTL+          | assertion of H_L                                     | OCK# and H_ADS#, until the negation of             |

|                  |                | H_LOCK# must                                         | be atomic.                                         |

| H_RCOMP          | I/O            | Host RCOMP: U                                        | sed to calibrate the Host AGTL+ I/O buffers.       |

|                  | Α              |                                                      |                                                    |

| H_REQ#[4:0]      | I/O            | Host Request Co                                      | mmand: Defines the attributes of the               |

|                  | AGTL+2X        | request. H_REQ#                                      | #[4:0] are transferred at 2x rate. Asserted by     |

|                  |                | the requesting ag                                    | gent during both halves of the Request             |

|                  |                |                                                      | t half the signals define the transaction type     |

|                  |                |                                                      | il that is sufficient to begin a snoop request.    |

|                  |                |                                                      | If the signals carry additional information to     |

|                  |                |                                                      | ete transaction type.                              |

| H_RS#[2:0]       | 0              | Host Response Status: Indicates the type of response |                                                    |

|                  | AGTL+          |                                                      | following the table:                               |

|                  |                | HRS[2:0]#                                            | Response type                                      |

|                  |                | 000                                                  | Idle state                                         |

|                  |                | 001                                                  | Retry response                                     |

|                  |                | 010                                                  | Deferred response                                  |

|                  |                | 011                                                  | Reserved (not driven by (G)MCH)                    |

|                  |                | 100                                                  | Hard Failure (not driven by (G)MCH)                |

|                  |                | 101                                                  | No data response                                   |

|                  |                | 110                                                  | Implicit Write back                                |

|                  |                | 111                                                  | Normal data response                               |

| IL OWING         | т              | II W. h C                                            | ·                                                  |

| H_SWING          | I              | , v                                                  | ing: These signals provide reference               |

| IL TDDV#         | A<br>O         |                                                      | the H_RCOMP circuits.                              |

| H_TRDY#          | ~              | -                                                    | dy: Indicates that the target of the               |

|                  | AGTL+          | processor transa                                     | ction can enter the data transfer phase.           |

# 4.1 Cantiga North Bridge -5

| Signal Name   | Туре         | Description                                                                 |

|---------------|--------------|-----------------------------------------------------------------------------|

| THERMTRIP#    | 0            | Connects between the Processor, (G)MCH and the ICH.                         |

|               | AGTL+        | Assertion of THERMTRIP# (Thermal Trip) indicates the                        |

|               |              | (G)MCH junction temperature has reached a level beyond                      |

|               |              | which damage may occur. Upon assertion of THERMTRIP#,                       |

|               |              | the (G)MCH will shut off its internal clocks (thus halting                  |

|               |              | program execution) in an attempt to reduce the (G)MCH core                  |

|               |              | junction temperature. To protect the (G)MCH, its core voltage               |

|               |              | (Vcc) must be removed following the assertion of                            |

|               |              | THERMTRIP#. Once activated, THERMTRIP# remains latched                      |

|               |              | until RSTIN# is asserted. While the assertion of the RSTIN#                 |

|               |              | signal will deassert THERMTRIP#, if the (G)MCH's junction                   |

|               |              | temperature remains at or above the trip level, THERMTRIP# will             |

|               |              | again be asserted.                                                          |

| Memory Channe | A Interface  |                                                                             |

| Signal Name   | Туре         | Description                                                                 |

| SA_BS[2:0]    | 0            | Bank Select: These signals define which banks are                           |

|               | SSTL-1.8/1.5 | selected within each SDRAM rank.                                            |

| SA_WE#        | 0            | Write Enable Control Signal: Used with SA_RAS# and                          |

|               | SSTL-1.8/1.5 | SA_CAS# (along with SA_CS#) to define the SDRAM commands.                   |

| SA_RAS#       | 0            | RAS Control Signal: Used with SA_CAS# and SA_WE#                            |

|               |              | (along with SA_CS#) to define the SDRAM commands.                           |

| SA_CAS#       | 0            | CAS Control Signal: Used with SA_RAS# and SA_WE#                            |

|               | SSTL-1.8/1.5 | (along with SA_CS#) to define the SDRAM commands.                           |

| SA_DM[7:0]    | 0            | Data Mask: These signals are used to mask individual                        |

|               | SSTL-1.8/1.5 | bytes of data in the case of a partial write, and to interrupt burst writes |

|               | 2x           | When activated during writes, the corresponding data                        |

|               |              | groups in the SDRAM are masked. There is one SA_DM[7:0] for                 |

|               |              | every data byte lane.                                                       |

| SA_DQS[7:0]   | I/O          | Data Strobes: SA_DQS[7:0] and its complement signal                         |

|               | SSTL-1.8/1.5 | group make up a differential strobe pair. The data is                       |

|               | 2x           | captured at the crossing point of SA_DQS[7:0] and its                       |

|               | 1            | SA_DQS[7:0]# during read and write transactions.                            |

# 4.1 Cantiga North Bridge -6

| SA_DQS#[7:0] | I/O          | Data Strobe Complements: These are the                          |

|--------------|--------------|-----------------------------------------------------------------|

|              | SSTL-1.8/1.5 | complementary strobe signals.                                   |

|              | 2x           |                                                                 |

| SA_DQ[63:0]  | I/O          | Data Bus: Channel A data signal interface to the SDRAM data bus |

|              | SSTL-1.8/1.5 |                                                                 |

|              | 2x           | A                                                               |

| SA_MA[14:0]  | 0            | Memory Address: These signals are used to provide the           |

|              | SSTL-1.8/1.5 | multiplexed row and column address to the SDRAM.                |

### Memory Channel A Interface(continued)

| Signal Name | Туре         | Description                                                   |  |

|-------------|--------------|---------------------------------------------------------------|--|

| SA_CK[1:0]  | 0            | SDRAM Differential Clock: Channel A SDRAM                     |  |

|             | SSTL-1.8/1.5 | Differential Clock signal-pair.                               |  |

|             |              | The crossing of the positive edge of SM_CKx and the           |  |

|             |              | negative edge of its complement SM_CKx# are used to           |  |

|             |              | sample the command and control signals on the SDRAM.          |  |

| SA_CK#[1:0] | 0            | SDRAM Inverted Differential Clock: Channel A SDRAM            |  |

|             | SSTL-1.8/1.5 | Differential Clock signal-pair complement.                    |  |

| SA_CKE[1:0] | 0            | Clock Enable: (1 per Rank) used to:                           |  |

|             | SSTL-1.8/1.5 | <ul> <li>Initialize the SDRAMs during power-up</li> </ul>     |  |

|             |              | Power-down SDRAM ranks                                        |  |

|             |              | Place all SDRAM ranks into and out of self-refresh during STR |  |

| SA_CS#[1:0] | 0            | Chip Select: (1 per Rank): Used to select particular          |  |

|             | SSTL-1.8/1.5 | SA_CS#[1:0] SDRAM components during the active state.         |  |

|             | P            | There is one Chip Select for each SDRAM rank                  |  |

| SA_ODT[1:0] | 0            | On Die Termination: Active Termination Control                |  |

|             | SSTL-1.8/1.5 |                                                               |  |

# 4.1 Cantiga North Bridge -7

| Memory Channe | 1            |                                                       |

|---------------|--------------|-------------------------------------------------------|

| Signal Name   | Туре         | Description                                           |

| SB_BS[2:0]    | 0            | Bank Select: These signals define which banks are     |

|               | SSTL-1.8/1.5 | selected within each SDRAM rank.                      |

| SB_WE#        | 0            | Write Enable Control Signal: Used with SB_RAS# and    |

|               | SSTL-1.8/1.5 | SB_CAS# (along with SB_CS#) to define the SDRAM       |

|               |              | commands.                                             |

| SB_RAS#       | 0            | RAS Control Signal: Used with SB_CAS# and SB_WE#      |

|               | SSTL-1.8/1.5 | (along with SB_CS#) to define the SDRAM commands.     |

| SB_CAS#       | 0            | CAS Control Signal: Used with SB_RAS# and SB_WE#      |

|               | SSTL-1.8/1.5 | (along with SB_CS#) to define the SDRAM commands.     |

| SB_DM[7:0]    | 0            | Data Mask: These signals are used to mask individual  |

|               | SSTL-1.8/1.5 | bytes of data in the case of a partial write, and to  |

|               | 2x           | interrupt burst writes.                               |

|               |              | When activated during writes, the corresponding data  |

|               |              | groups in the SDRAM are masked. There is one          |

|               |              | SB_DM[7:0] for every data byte lane.                  |

| SB_DQS#[7:0]  | I/O          | Data Strobe Complements: These are the                |

|               | SSTL-1.8/1.5 | complementary strobe signals.                         |

|               | 2x           |                                                       |

| SB_DQS[7:0]   | I/O          | Data Strobes: SB_DQS[7:0] and its complement signal   |

|               | SSTL-1.8/1.5 | group make up a differential strobe pair. The data is |

|               | 2x           | captured at the crossing point of SB_DQS[7:0] and its |

|               |              | SB_DQS[7:0]# during read and write transactions.      |

| SB_MA[14:0]   | 0            | Memory Address: These signals are used to provide the |

|               | SSTL-1.8/1.5 | multiplexed row and column address to the SDRAM.      |

# 4.1 Cantiga North Bridge -8

| Memory Channe  | el B Interface(co | ontinued)                                                    |

|----------------|-------------------|--------------------------------------------------------------|

| Signal Name    | Туре              | Description                                                  |

| SB_DQ[63:0]    | I/O               | Data Bus: Channel B data signal interface to the SDRAM       |

|                | SSTL-1.8/1.5      | data bus.                                                    |

|                | 2x                |                                                              |

| SB_CK[1:0]     | 0                 | SDRAM Differential Clock: Channel B SDRAM                    |

|                | SSTL-1.8/1.5      | Differential Clock signal-pair. The crossing of the positive |

|                |                   | edge of SM_CKx and the negative edge of its complement       |

|                |                   | SM_CKx# are used to sample the command and control           |

|                |                   | signals on the SDRAM.                                        |

| SB_CK#[1:0]    | 0                 | SDRAM Inverted Differential Clock: Channel B SDRAM           |

|                | SSTL-1.8/1.5      | Differential Clock signal-pair complement.                   |

| SB_CKE[1:0]    | 0                 | Clock Enable: (1 per Rank): Used to initialize the           |

|                | SSTL-1.8/1.5      | SDRAMs during power-up, power-down SDRAM ranks,              |

|                |                   | place all SDRAM ranks into and out of self-refresh during    |

|                |                   | STR.                                                         |

| SB_CS#[1:0]    | 0                 | Chip Select: (1 per Rank): Used to select particular         |

|                | SSTL-1.8/1.5      | SDRAM components during the active state. There is one       |

|                |                   | Chip Select for each SDRAM rank.                             |

| SB_ODT[1:0]    | 0                 | On Die Termination: Active Termination Control               |

|                | SSTL-1.8/1.5      |                                                              |

| Memory Referen | nce and Comper    | isation                                                      |

| Signal Name    | Туре              | Description                                                  |

| SM_RCOMP       | I                 | System Memory Impedance Compensation: Refer                  |

|                | А                 | Montevina Platform Design Guide for implementation           |

| SM DCOMP#      | т                 | Contraction Manual Line Contraction Defen                    |

| memory referen | ee and compe | isation                                            |

|----------------|--------------|----------------------------------------------------|

| Signal Name    | Туре         | Description                                        |

| SM_RCOMP       | I            | System Memory Impedance Compensation: Refer        |

|                | А            | Montevina Platform Design Guide for implementation |

| SM_RCOMP#      | Ι            | System Memory Impedance Compensation: Refer        |

|                | А            | Montevina Platform Design Guide for implementation |

| SM_RCOMP_V     | Ι            | System Memory pull up impedance compensation       |

|                | А            |                                                    |

| SM_RCOMP_V     | Ι            | System Memory pull down impedance                  |

|                | А            | compensation                                       |

| SM_VREF        | Ι            | System Memory Reference Voltage for all data and   |

|                | А            | data strobe signals.                               |

| SM_REXT        | IO           | Constant circuit reference for clocks.             |

|                | А            |                                                    |

# 4.1 Cantiga North Bridge -9

### PCI Express Based Graphics Interface Signals

| Signal Name   | Туре        | Description                                               |

|---------------|-------------|-----------------------------------------------------------|

| PEG_COMPI     | Ι           | PEG_COMPI PCI Express Graphics Input Current Compensation |

|               | А           |                                                           |

| PEG_COMPO     | Ι           | PCI Express Graphics Output Current and Resistance        |

|               | А           | Compensation                                              |

| PEG_RX[15:0]  | Ι           | PCI Express Graphics Receive Differential Pair            |

| PEG_RX#[15:0] | PCI Express |                                                           |

| PEG_TX[15:0]  | 0           | PCI Express Graphics Transmit Differential Pair           |

| PEG_TX#[15:0] | PCI Express |                                                           |

### DMI – (G)MCH to ICH Serial Interface

| DMI – (G)MCH t | DMI – (G)MCH to ICH Serial Interface |                                                    |  |  |  |

|----------------|--------------------------------------|----------------------------------------------------|--|--|--|

| Signal Name    | Туре                                 | Description                                        |  |  |  |

| DMI_RXN[3:0]   | Ι                                    | DMI input from ICH: Direct Media Interface receive |  |  |  |

| DMI_RXP[3:0]   | PCI                                  | differential pair                                  |  |  |  |

|                | Express                              |                                                    |  |  |  |

| DMI_TXN[3:0]   | 0                                    | DMI output to ICH: Direct Media Interface transmit |  |  |  |

| DMI_TXP[3:0]   | PCI                                  | differential pair                                  |  |  |  |

|                | Express                              |                                                    |  |  |  |

| CRT DAC Signals |      |                                                               |  |

|-----------------|------|---------------------------------------------------------------|--|

| Signal Name     | Туре | Description                                                   |  |

| CRT_RED         | 0    | RED Analog Video Output: This signal is a CRT analog video    |  |

|                 | A    | output from the internal color palette DAC.                   |  |

| CRT_GREEN       | 0    | GREEN Analog Video Output: This signal is a CRT analog video  |  |

|                 | А    | output from the internal color palette DAC.                   |  |

| CRT_BLUE        | 0    | BLUE Analog Video Output: This signal is a CRT analog video   |  |

|                 | А    | output from the internal color palette DAC.                   |  |

| CRT_TVO_IREF    | 0    | Resistor Set and TV Reference Current: Set point resistor for |  |

|                 | А    | the internal color palette DAC and TV reference current.      |  |

# 4.1 Cantiga North Bridge -10

| CRT DAC Signa | ls(continued) |                                                                 |

|---------------|---------------|-----------------------------------------------------------------|

| Signal Name   | Туре          | Description                                                     |

| CRT_VSYNC     | 0             | CRT Vertical Synchronization: This signal is used as the        |

|               | HVCMOS        | vertical sync (polarity is programmable).                       |

| CRT_HSYNC     | 0             | CRT Horizontal Synchronization: This signal is used as the      |

|               | HVCMOS        | horizontal sync (polarity is programmable) or "sync interval".  |

| CRT_IRTN      | 0             | Resistor Set: Set point resistor for the internal color palette |

|               | А             | DAC                                                             |

| Analog TV-out Signals |      |                                                        |

|-----------------------|------|--------------------------------------------------------|

| Signal Name           | Туре | Description                                            |

| TV_DCONSEL[1          | 0    | TVD-connector Select: Selects appropriate full-voltage |

|                       | COD  | discernment signals for TV-out D-connector.            |

| TVA_DAC               | 0    | TVDAC Channel A Output: Can map to any one of the      |

|                       | А    | following:                                             |

|                       |      | Composite Video, Blank, and Sync (CVBS)                |

|                       |      | Component Pb                                           |

| TVB_DAC               | 0    | TVDAC Channel B Output: Can map to any one of the      |

|                       | А    | following:                                             |

|                       |      | • Svideo - Y                                           |

|                       |      | Component Y                                            |

| TVC_DAC               | 0    | TVDAC Channel C Output: Can map to any one of the      |

|                       | Α    | following:                                             |

|                       |      | • Svideo - C                                           |

|                       |      | Component Pr                                           |

| TV_RTN                | 0    | Current Return for TV DAC Channel A/B/C: Connect to    |

|                       | А    | ground on board                                        |

# 4.1 Cantiga North Bridge -11

| LVDS Signals |        |                                                              |

|--------------|--------|--------------------------------------------------------------|

| Signal Name  | Туре   | Description                                                  |

|              |        | LDVS Channel A                                               |

| LVDSA_CLK    | 0      | LVDS Channel A differential clock output - positive          |

|              | LVDS   |                                                              |

| LVDSA_CLK#   | 0      | LVDS Channel A differential clock output – negative          |

|              | LVDS   |                                                              |

| LVDSA_DATA#  | 0      | LVDS Channel A differential data output – negative           |

|              | LVDS   |                                                              |

| LVDSA_DATA[  | 0      | LVDS Channel A differential data output – positive           |

|              | LVDS   |                                                              |

|              |        | LDVS Channel B                                               |

| LVDSB_CLK    | 0      | LVDS Channel B differential clock output - positive          |

|              | LVDS   |                                                              |

| LVDSB_CLK#   | 0      | LVDS Channel B differential clock output - negative          |

|              | LVDS   |                                                              |

| LVDSB_DATA#  | 0      | LVDS Channel B differential data output - negative           |

|              | LVDS   |                                                              |

| LVDSB_DATA[  | 0      | LVDS Channel B differential data output – positive           |

|              | LVDS   |                                                              |

|              |        | Panel Power and Backlight Control                            |

| L_BKLT_CTRL  | 0      | Panel Backlight Brightness Control:                          |

|              | HVCMOS | Panel brightness control.                                    |

|              |        | This signal is also called VARY_BL in the CPIS specification |

|              |        | and is used as the PWM Clock input signal.                   |

| L_BKLT_EN    | 0      | LVDS Backlight Enable:                                       |

|              | HVCMOS | Panel backlight enable control.                              |

|              |        | This signal is also called ENA_BL in the CPIS specification  |

|              |        | and is used to gate power into the backlight circuitry.      |

| L_VDD_EN     | 0      | LVDS Panel Power Enable:                                     |

|              | HVCMOS | Panel power control enable control.                          |

|              |        | This signal is also called VDD_DBL in the CPIS specification |

|              |        | and is used to control the VDC source to the panel logic.    |

# 4.1 Cantiga North Bridge -12

| LVDS Reference Signals |     |                              |

|------------------------|-----|------------------------------|

| LVDS_IBG               | I/O | LVDS Reference Current       |

|                        | Ref |                              |

| LVDS_VBG               | 0   | Leave as NC                  |

|                        | А   |                              |

| LVDS_VREFH             | Ι   | Must be connected to ground. |

|                        | Ref |                              |

| LVDS_VREFL             | Ι   | Must be connected to ground. |

|                        | Ref |                              |

| Display Data Channel (DDC) and GMBUS Support |      |                                                              |  |

|----------------------------------------------|------|--------------------------------------------------------------|--|

| Signal Name                                  | Туре | Description                                                  |  |

| CRT_DDC_CLK                                  | I/O  | CRT DDC clock monitor control support                        |  |

|                                              | COD  |                                                              |  |

| CRT_DDC_DAT                                  | I/O  | CRT DDC Data monitor control support                         |  |

|                                              | COD  |                                                              |  |

| L_CTRL_CLK                                   | I/O  | Control signal (clock) for External SSC clock chip control – |  |

|                                              | COD  | optional                                                     |  |

| L_CTRL_DATA                                  | I/O  | Control signal (data) for External SSC clock chip control –  |  |

|                                              | COD  | optional                                                     |  |

| L_DDC_CLK                                    | I/O  | EDID support for flat panel display                          |  |

|                                              | COD  |                                                              |  |

| L_DDC_DATA                                   | I/O  | EDID support for flat panel display                          |  |

|                                              | COD  |                                                              |  |