| 1. DEFINITION OF CONNECTORS & SWITCHES | P.2  |

|----------------------------------------|------|

| 2. LOCATION OF SWITCHES & CONNECTORS   | P.3  |

| 3. MAJOR COMPONENTS                    | P.5  |

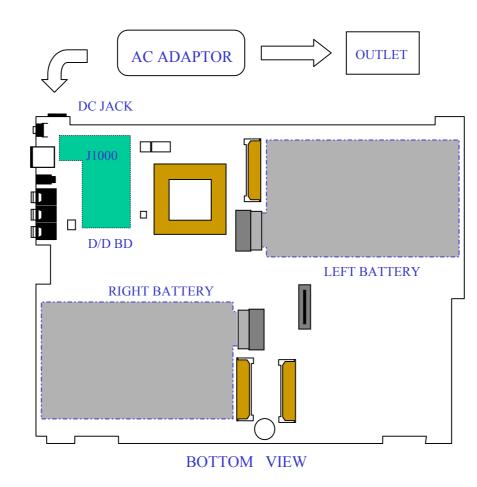

| 4. LOCATION OF MAJOR COMPONENTS        | P.6  |

| 5. PIN DESCRIPTIONS OF MAJOR CHIPS     | P.8  |

| 6. SWITCH & JUMPERS SETTING            | P.30 |

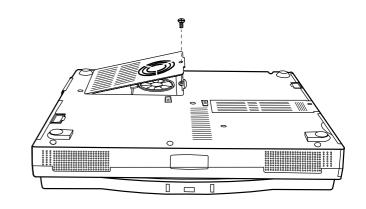

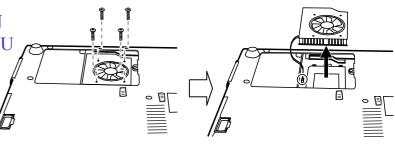

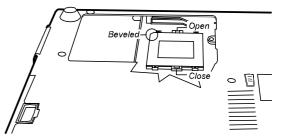

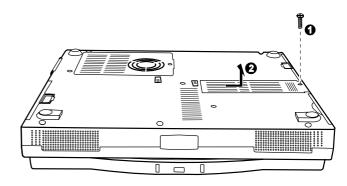

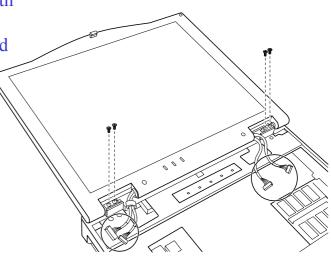

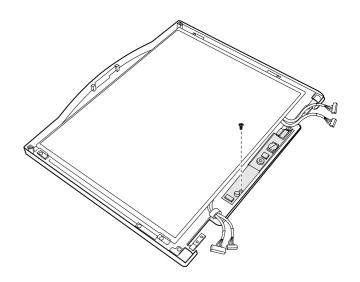

| 7. ASSEMBLY & DISASSEMBLY              | P.31 |

| 8. MAINTENANCE DIAGNOSTICS             | P.48 |

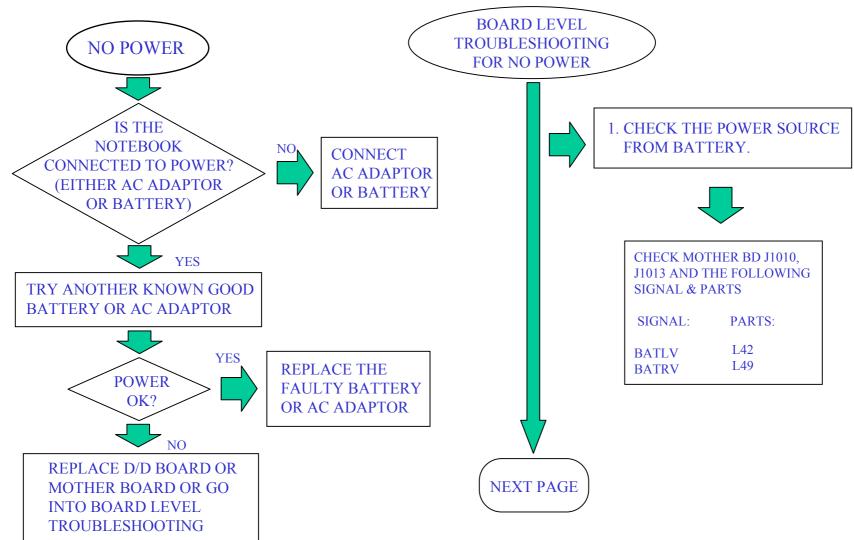

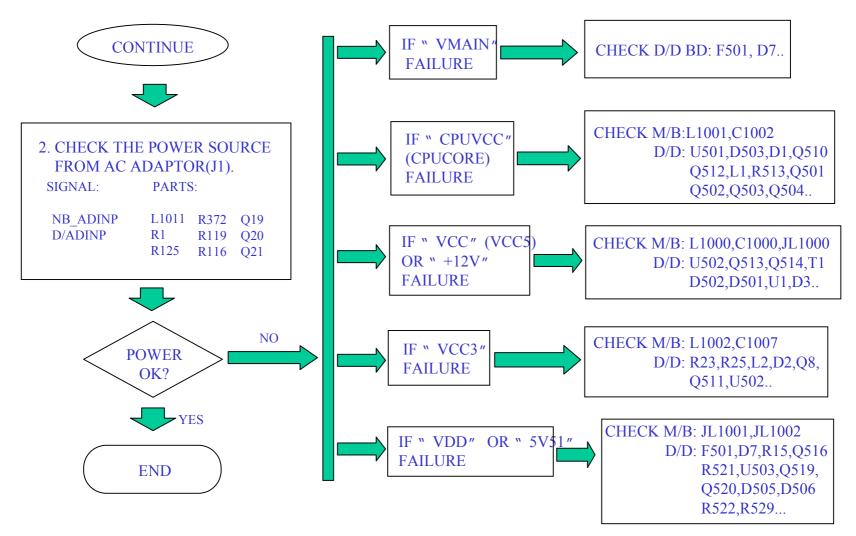

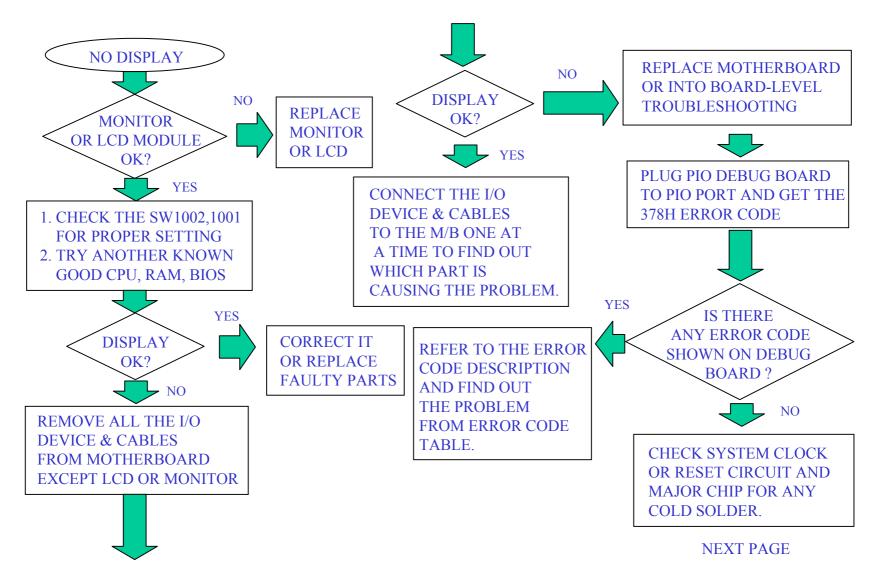

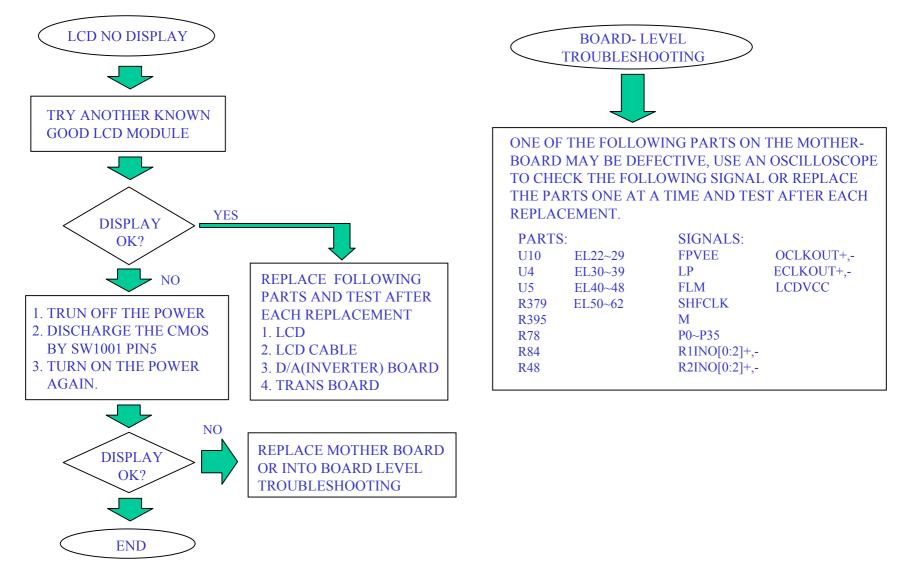

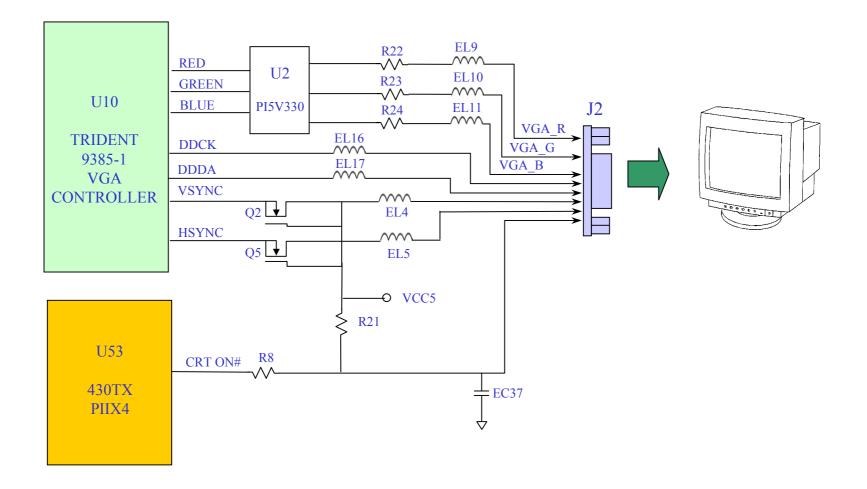

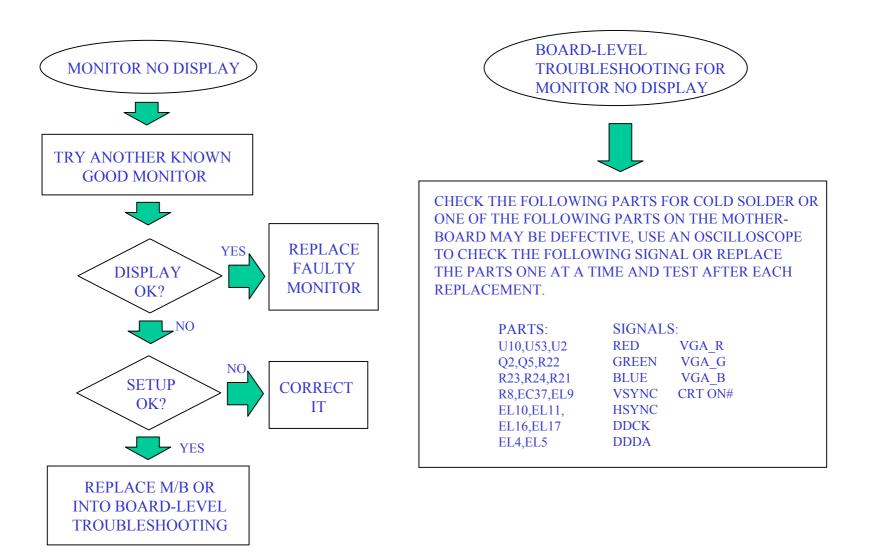

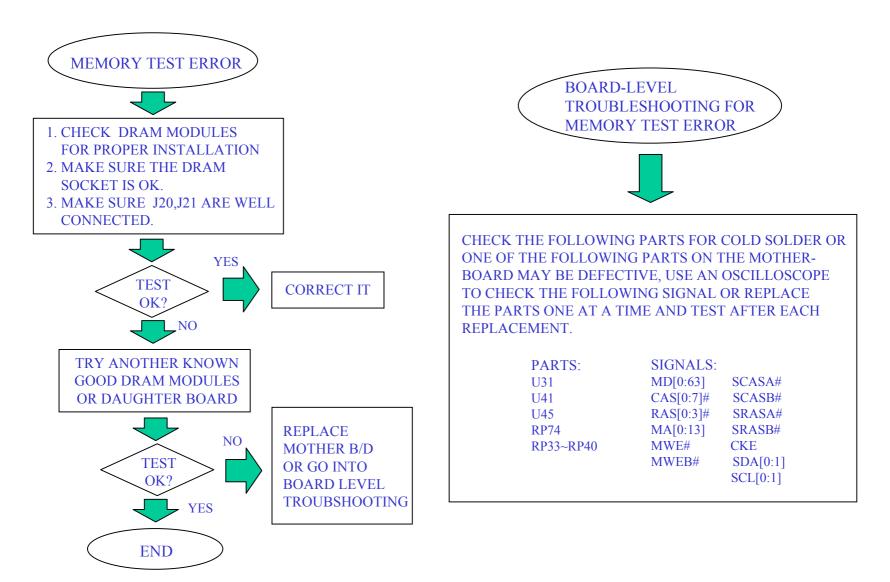

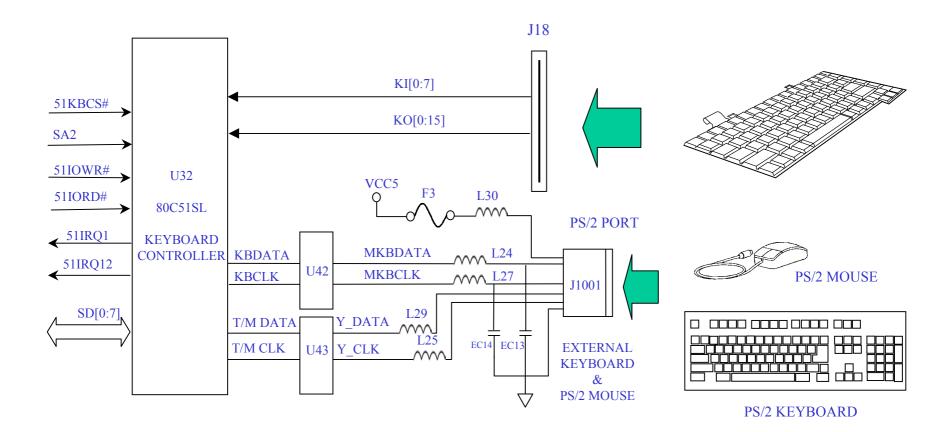

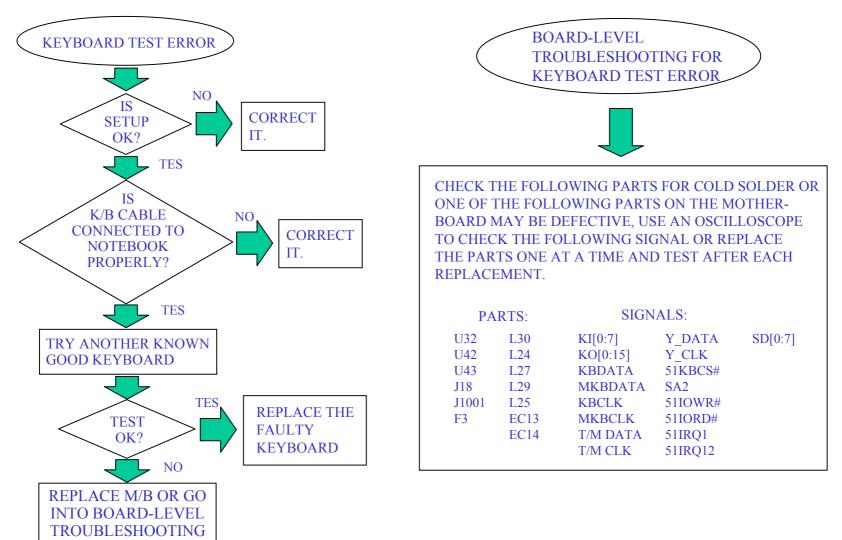

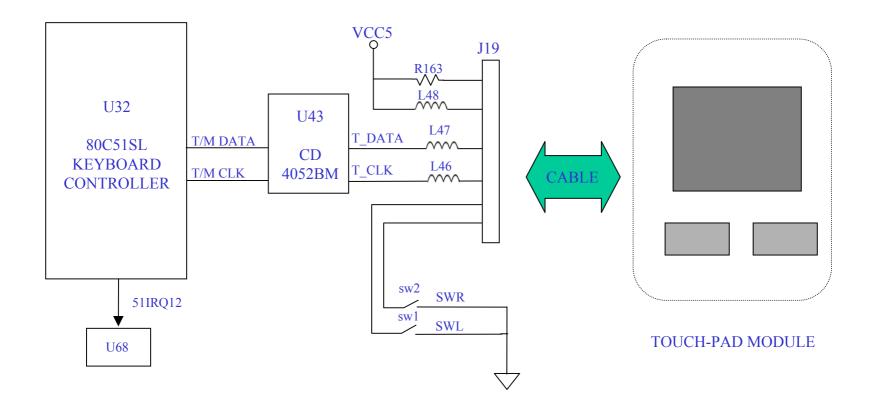

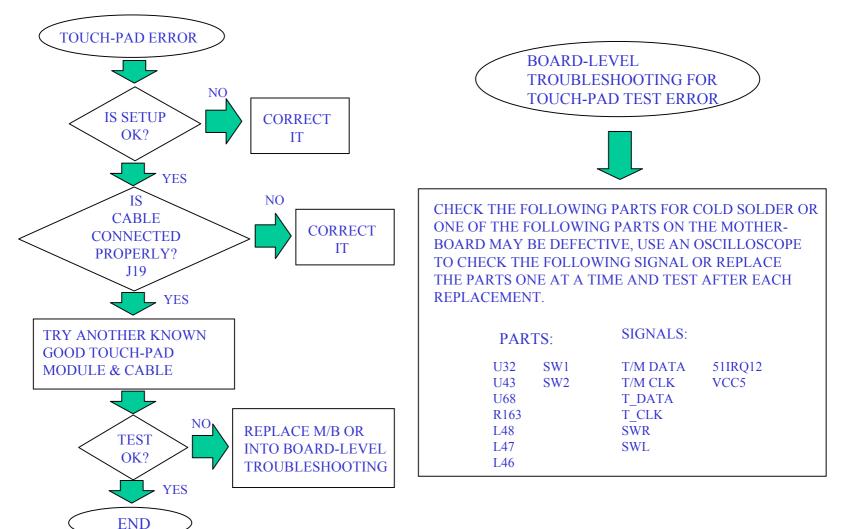

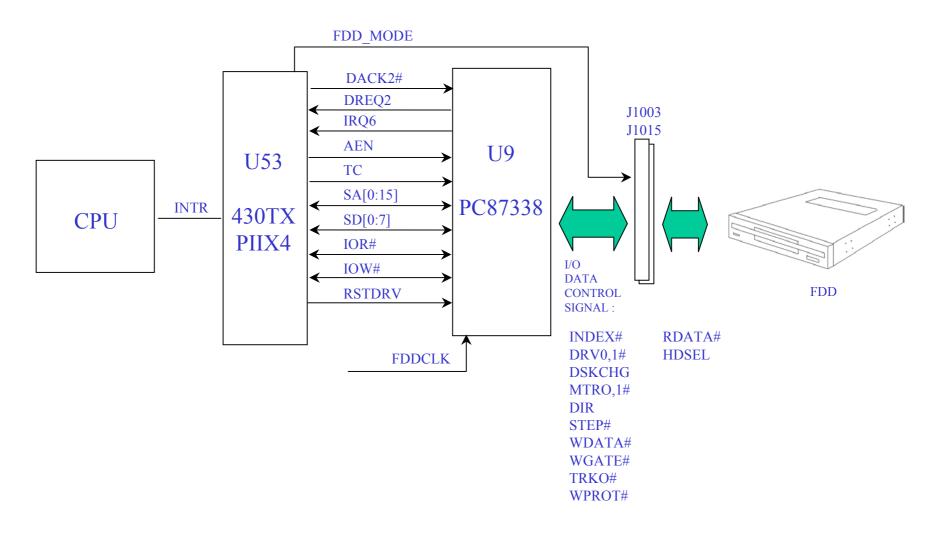

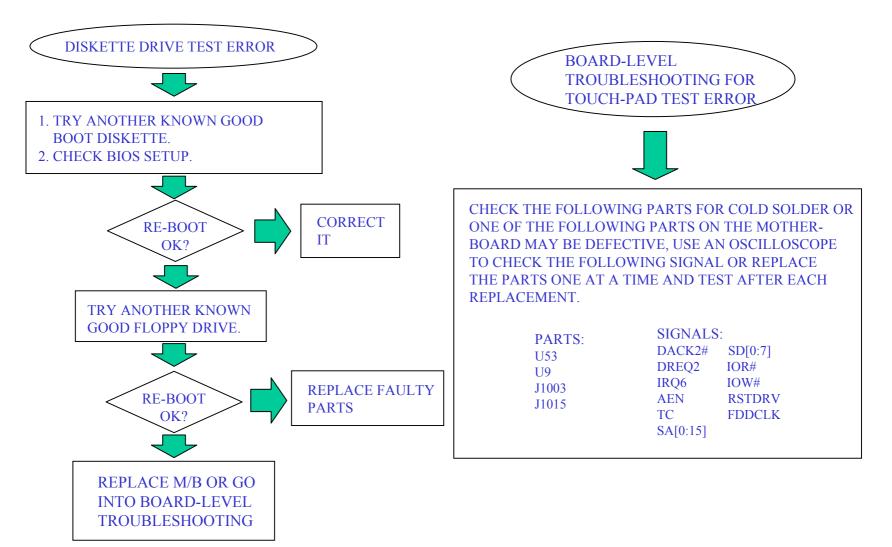

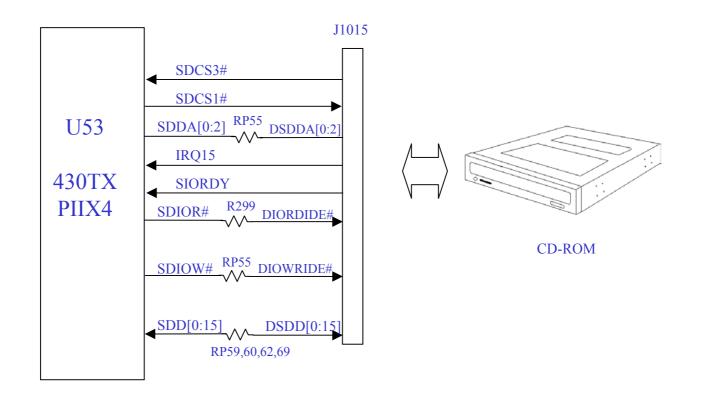

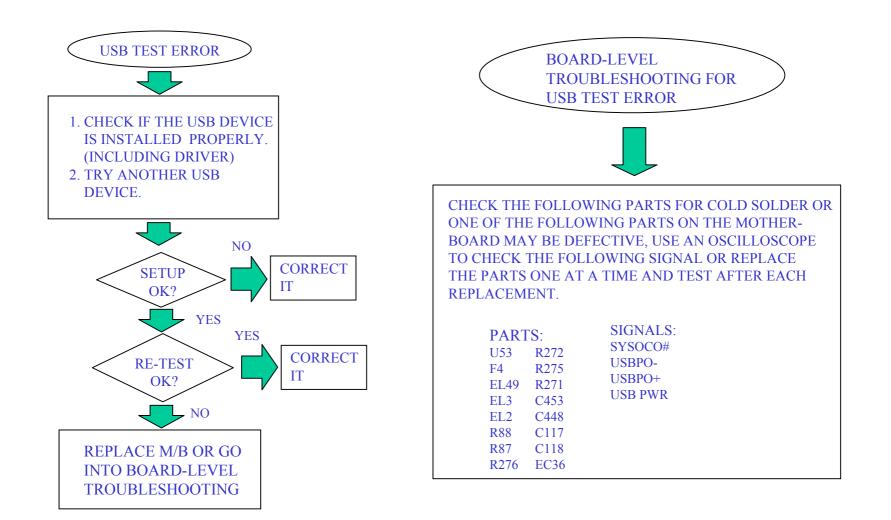

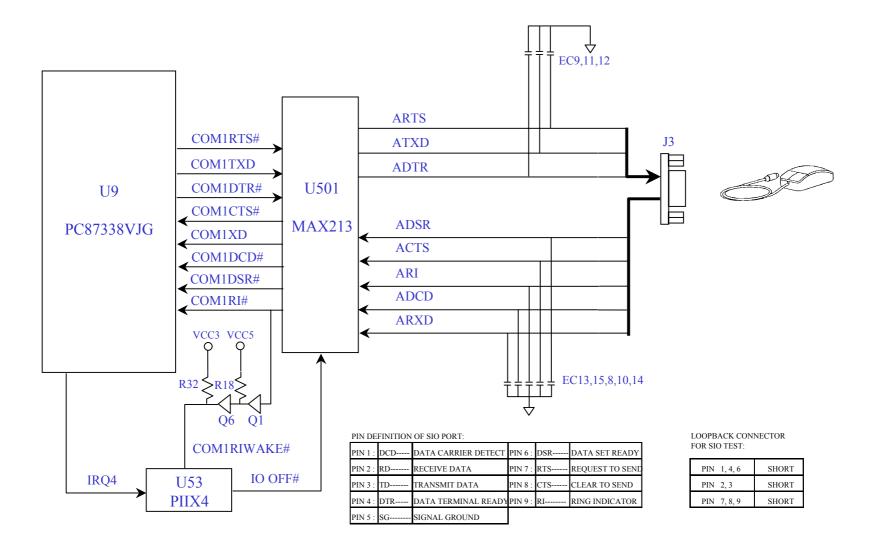

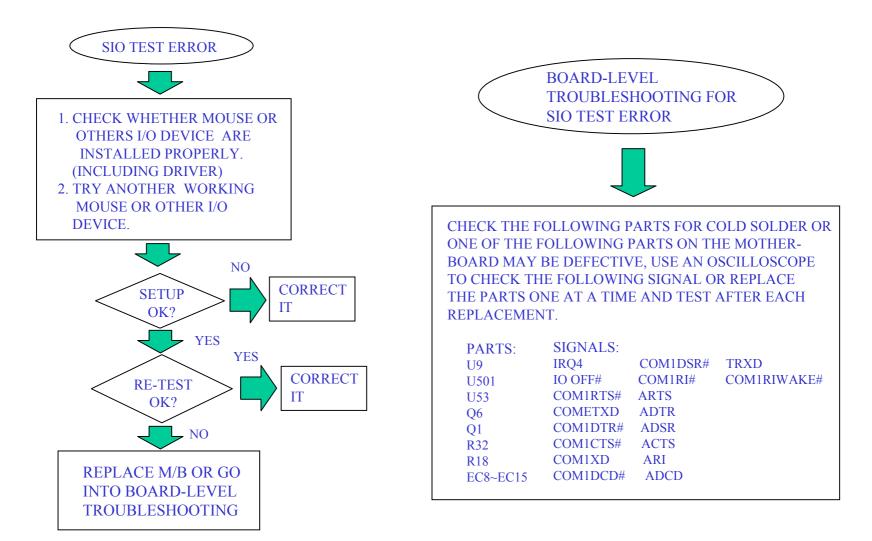

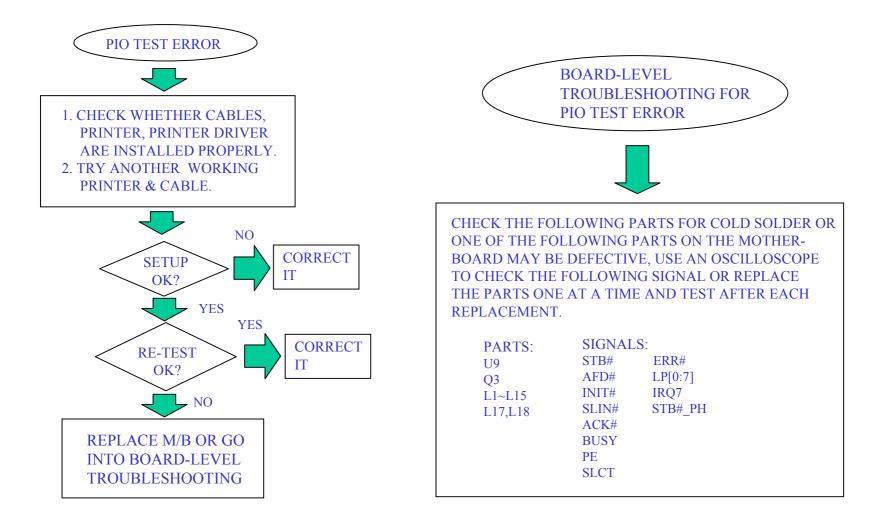

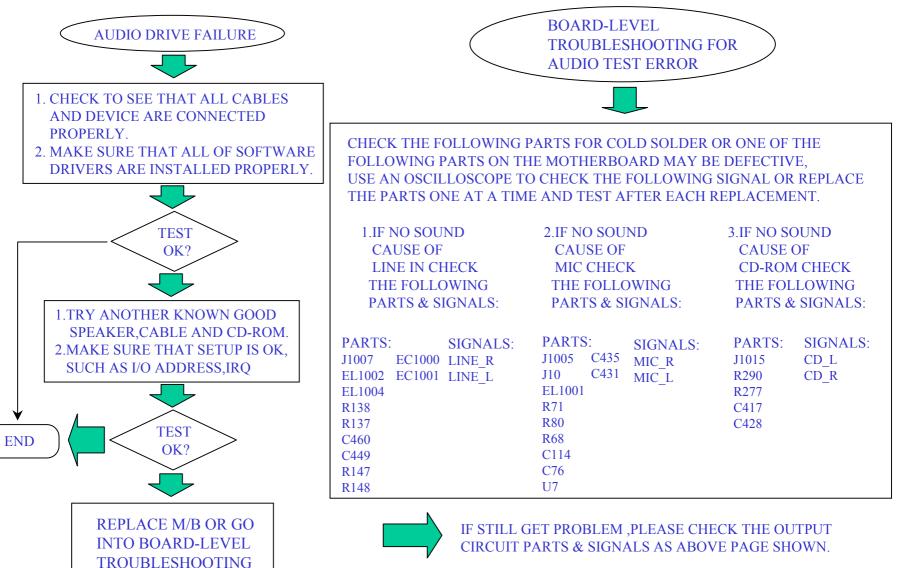

| 9. TROUBLE SHOOTING                    | P.51 |

| 10. SPARE PARTS LIST                   | P.83 |

| 11. EXPLODED VIEWS AND CIRCUIT DIAGRAM |      |

1

## **1. DEFINITION OF CONNECTORS & SWITCHS**

- J1 . POWER CONNECTOR

- J2 . VGA CONNECT

- J3 . RS232/SIO

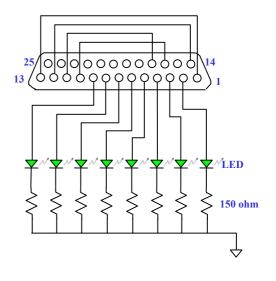

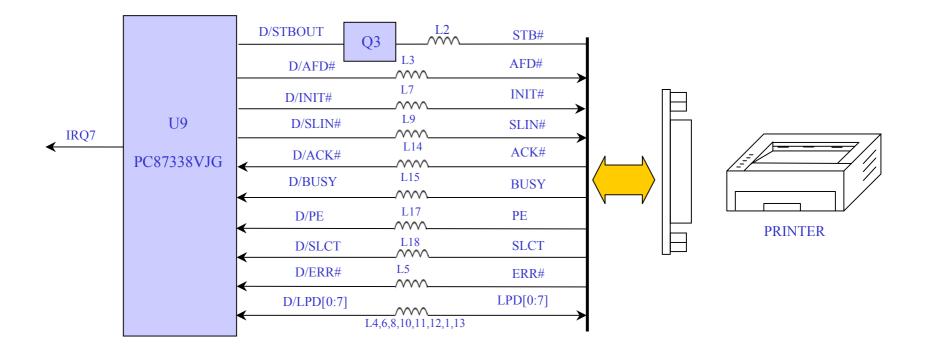

- J4 . PIO CONNECTOR

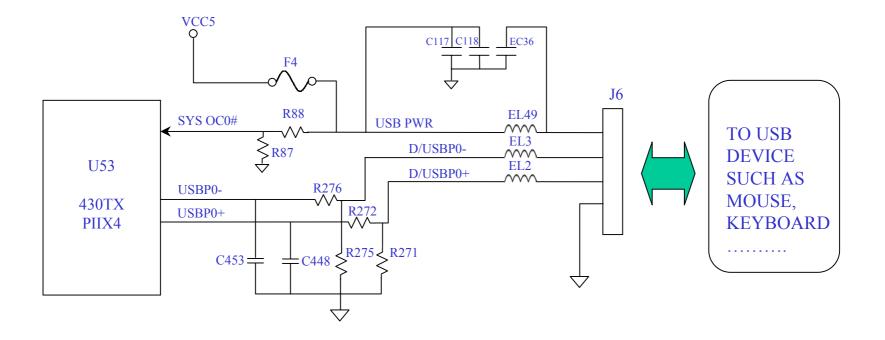

- J6. USB PORT CONNECTOR

- J7. DOCKINK STATION CONNECTOR

- J8. INTERNAL LEFT SPEAKER CONNECTOR

- J9 . INTERNAL RIGHT SPEAKER CONNECTOR

- J10.INTERNAL MICROPHONE CONNECTOR

- J11.UPPER LED CARD CONNECTOR

- J12.COVER SW CONNECTOR

- J13.BACKLIGHT CONNECTOR

- J14.LOWER LED CONNECTOR

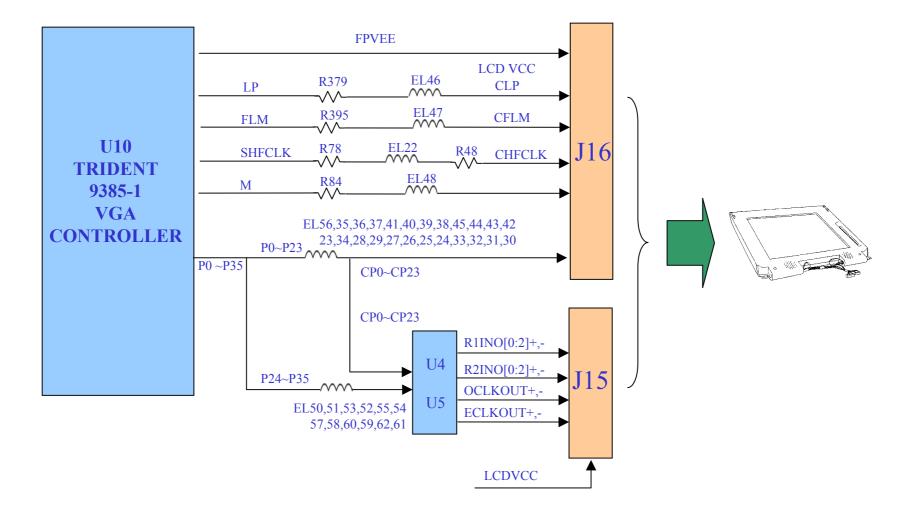

- J15.LVDS CARD CONNECTOR

- J16.LEGACY LCD PANEL CONNECTOR

- J18.INTERNAL KEYBOARD CONNECTOR

- J19.TOUCHPADE CONNECTOR

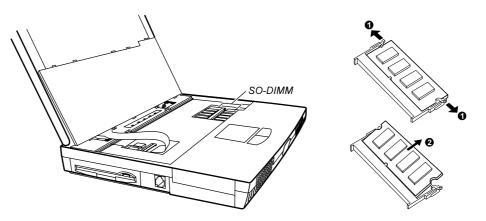

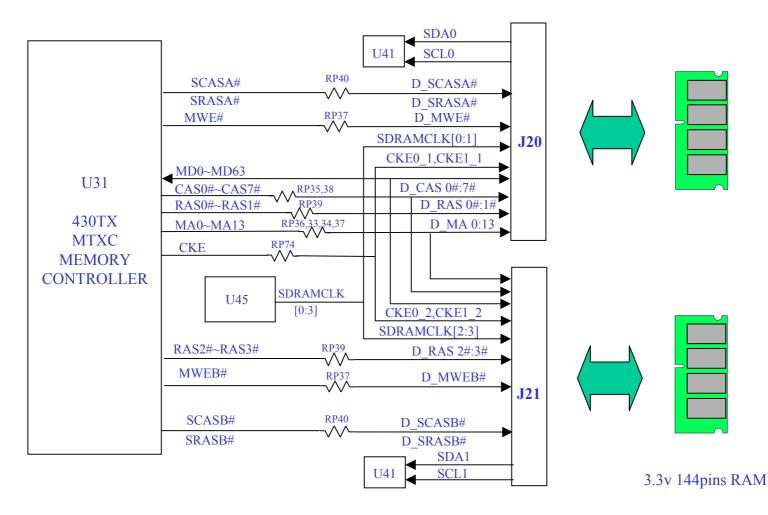

- J20, J21.144-PIN DIMM SOCKETS

- J22.PCCARD CONNECTOR

- J23.INTERNAL CAMERA CONNECTOR

- J1000.D/D BOARD CONNECTOR

- J1001.PS/2 KEYBOARD/MOUSE CONNECTOR

- J1003, J1015. FDD/MO/HDD2 CONNECTORS

- J1005.EXTERNAL MICROPHONE CONNECTOR

- J1007.LINE-IN CONNECTOR

- J1008.TV IN/OUT TRANSLATION CARD CONNECTOR

- J1009.LINE-OUT CONNECTOR

- J1010.LEFT BATTERY CONNECTOR

- J1012.FAX/MODEM/VOICE CONNECTOR

- J1013.RIGHT BATTERY CONNECTOR

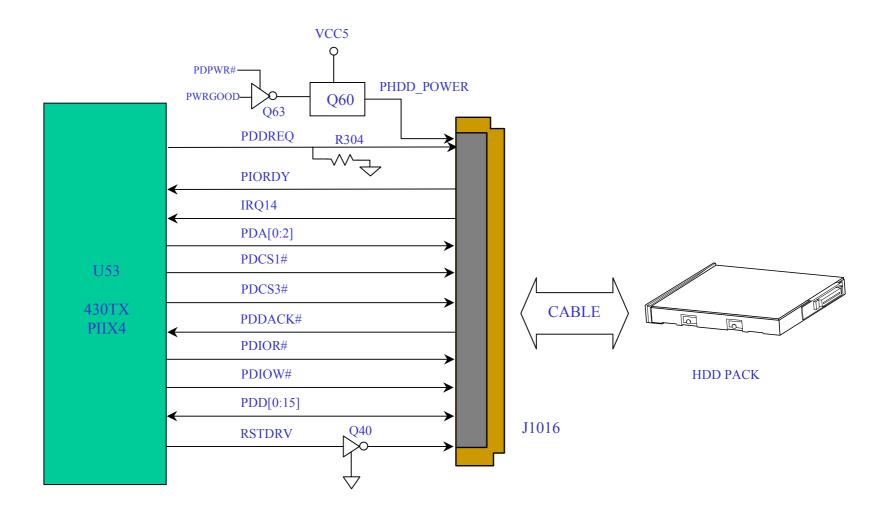

- J1016.PRIMARY HDD CONNECTOR

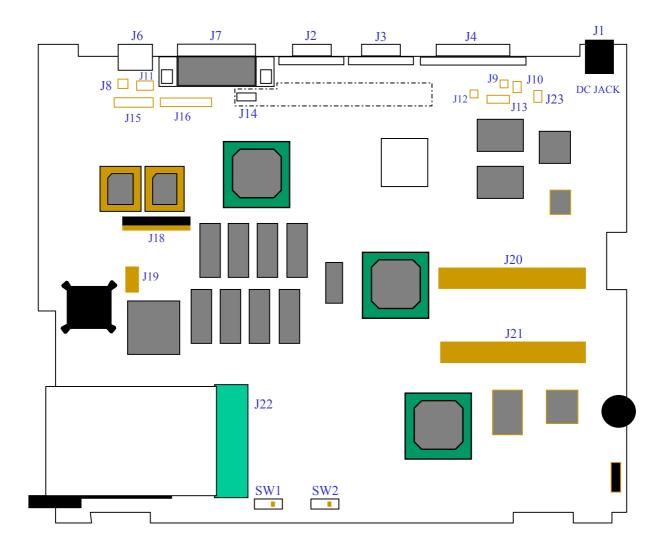

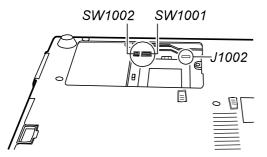

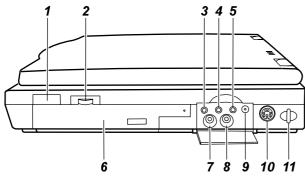

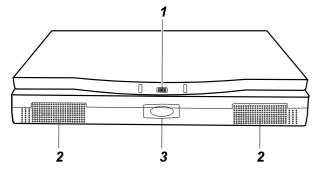

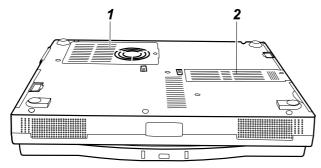

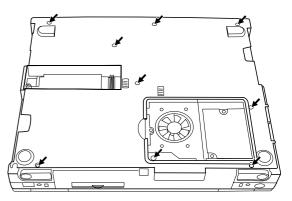

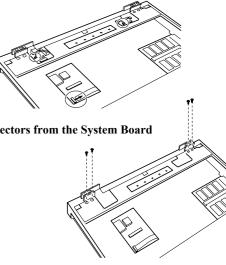

# 2. LOCATION OF CONNECTORS & SWITCHES (A)

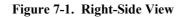

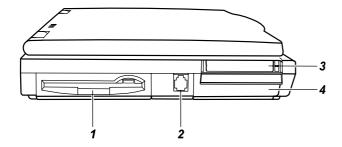

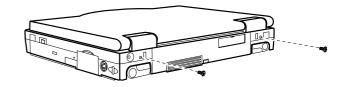

# 2. LOCATION OF CONNECTORS & SWITCHES (B)

# **3. MAJOR COMPONENTS**

- 1. U9 SUPER I/O CONTROLLER (PC87338VJG)

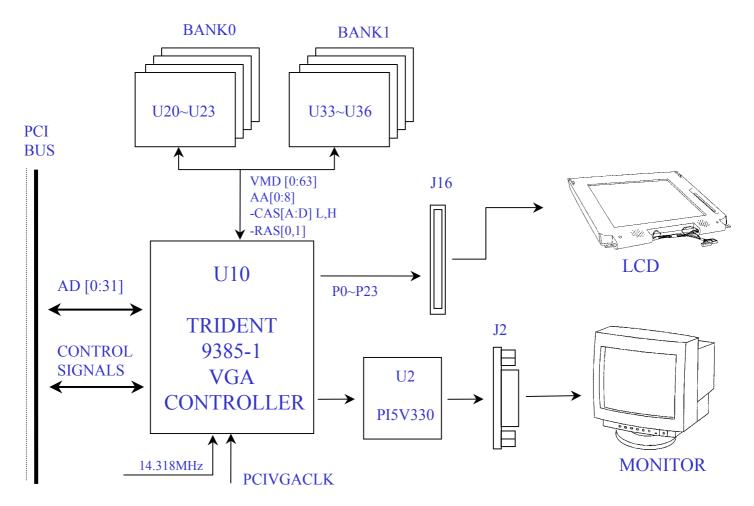

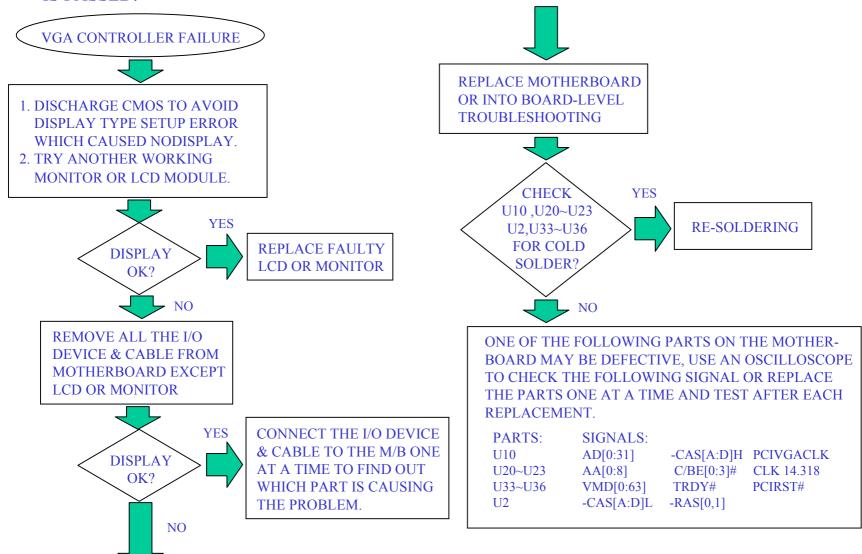

- 2. U10 LCD CRT & TV 64 BIT MUL-TIMEDIA FLAT PANEL CONTROLLER (CYBER9385/2)

- 3. U6,U13 512K L2 CACHE

- 4. U14 KEYBOARD BIOS (27C256)

- 5. U15 256K FLASH ROM (281020)

- 6. U20~U23,U33~U36 4MB VIDEO MEMORY (416C256)

- 7. U31 MTXC (82439TX)

8.U32 KEYBOARD CONTROLLER(80C51SL)

9. U38 CARDBUS CONTROLLER (OZ6832)

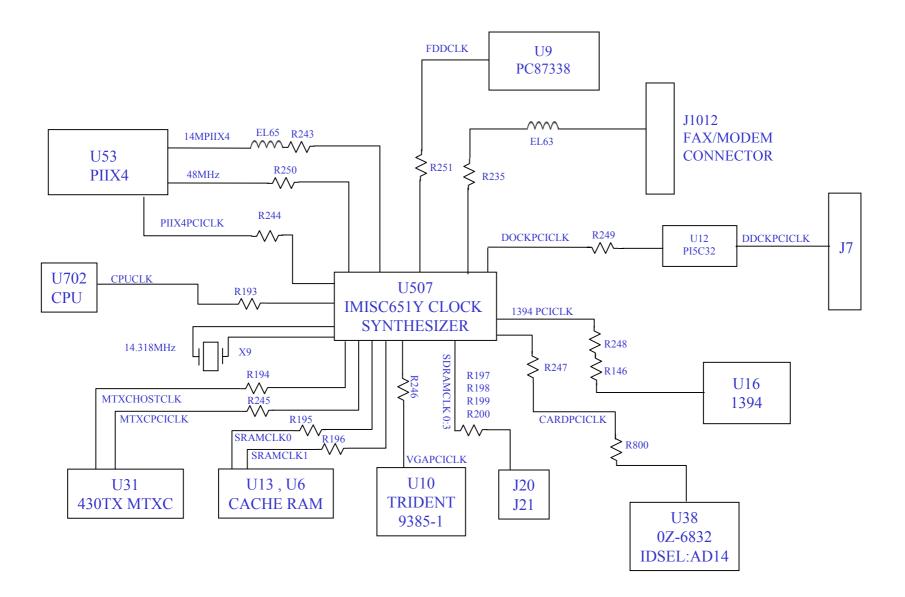

10.U45 CLOCK SYNTHESIZER(W48S67-02)

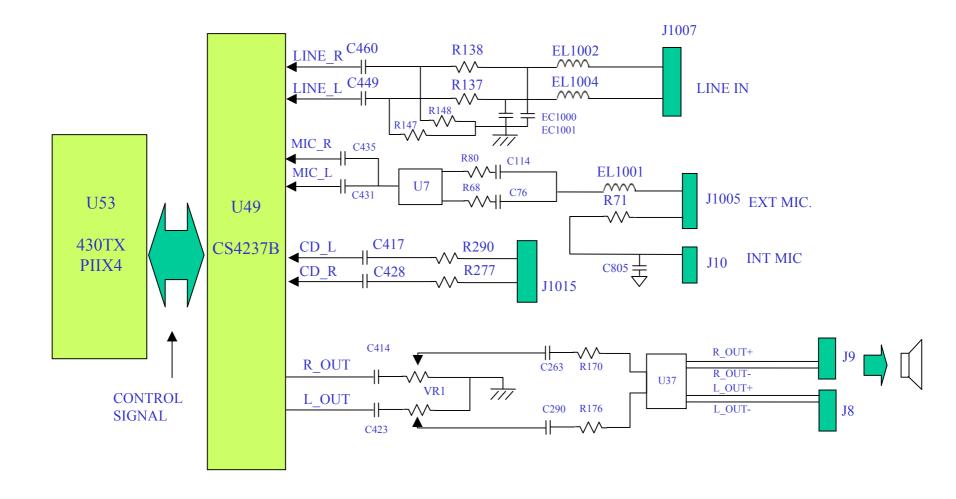

- 11. U49 AUDIO CONTROLLER (CS4237B)

- 12. U53 PIIX4 (82371AB)

- 13. U702 CPU (P55CLM ,TILLAMOOK, OR COMPATIBLE CPU)

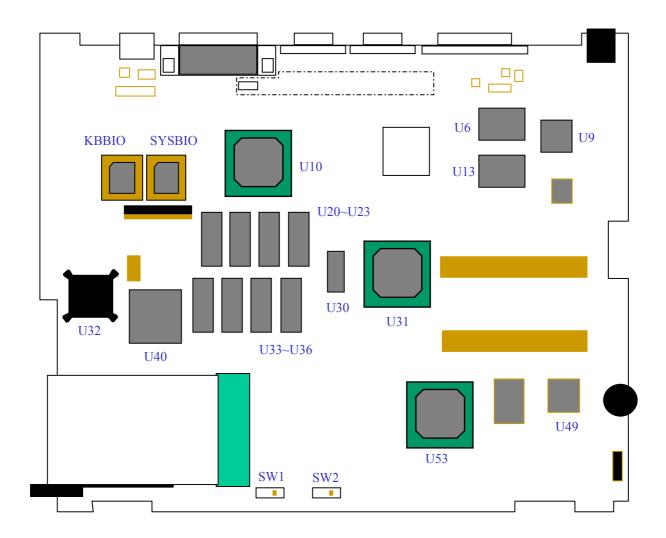

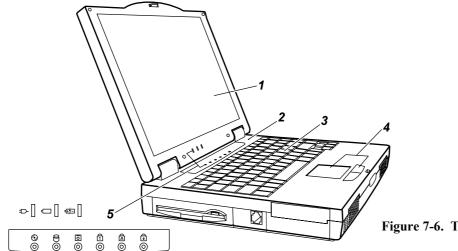

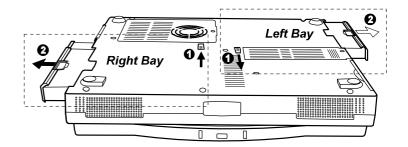

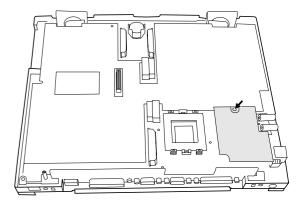

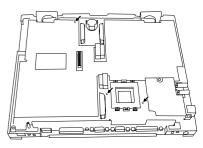

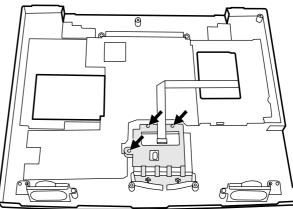

## 4. LOCATION OF MAJOR COMPONENTS (A)

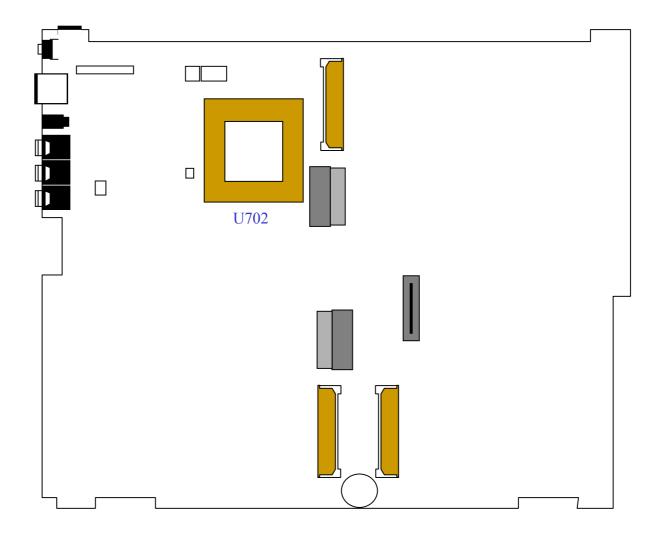

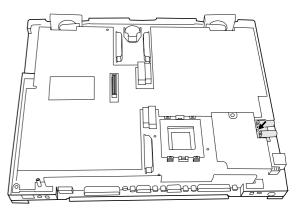

## 4. LOCATION OF MAJOR COMPONENTS (B)

### 5. PIN DESCRIPTIONS OF MAJOR COMPONENTS 5.1 PENTIUM MICROPROCESSOR (P54LM)-1

| SYMBOL    | TY PE | DESCRIPTION                                                |

|-----------|-------|------------------------------------------------------------|

| A 20M #   | I     | w hen the address bit 20 mask pin is active, the 20 (A20)  |

|           |       | PENTIUNM M CORPROCESSOR MASKS PHYSICAL ADDRES BI           |

|           |       | BEFORE PERFORM ING A LOOKUP TO THE INTERNAL CACHE OR       |

|           |       | EM ULATES THE ADDRESS W RAPAROUND AT THE AM B              |

|           |       | DR IVING A MEMORY BUS CYCLE ONTO THE BUSES.A20M #          |

|           |       | BOUNDARY THAT OCCUS ON THE 8086,8088.                      |

| A 31 A 5  | ΙQ    | A 31 A 3 COM PRISE THR PENTIUM E ,ICROPROCESSOR S ADDRES   |

| A4:A3     | 0     | BUS.                                                       |

| ADS#      | IO    | W HEN ACTIVE ,THE ADDRESS STATUS OUTPUT INDICCATES         |

|           |       | THAT A VALID BUS CYCLE DEFINITION AND ADDRESS ARE          |

|           |       | AVALABLE ON THE BUS CYCLE DEFINITION AND BUS LINES.        |

| AHOLD     | I     | THE ADDRESS HOLD REQUEST INPUT ALLOW S ANOTHER BUS MAST-   |

|           |       | ER ACCESS TO PENTIUM M ICROPROCESSOR S ADDRESS BUS FOR A   |

|           |       | CACHE INVALIDATION, BACK INVALIDATION, OR INQUIRE CYCLE.   |

| AP        | ΙΌ    | THE PENTIUM PROCESS GENERATES ADDRESS PARIFY DURING        |

|           |       | M EM ORY W RIFE OPERATIONS AND CHECK ADDRESS PARIFY        |

|           |       | DUR ING CACHE INVALIDATION CYCLES (ADDRESS BUS SNOOPING ). |

| APCHK#    | 0     | THE PENTION PROCESS ASSERTS THE ADDRES PARITY CHECK        |

|           |       | OUTPUT W HEN AN ADDRES BUS PARITY ERROD IS DETECTED        |

|           |       | APCHK# IS ASSERTED 2 CLOCK CYCLES AFTER EADS# IS           |

|           |       | SAM PLE ACTIVE . APCHK\$ REM A IN ACTIVE FOR ON CLOCK      |

|           |       | CYCLE.                                                     |

| [APICHEN] | ΙO    | APIC ENABLE.                                               |

| OR PICD1  |       |                                                            |

| BE0#      | 0     | BYTE ENABLE PATHO (D7D0).                                  |

| BE1#      | 0     | BYTE ENABLE PATH1 (D15D8).                                 |

| BE2#      | 0     | BYTE ENABLE, PATH 2 (D23D16).                              |

| BE3#      | 0     | BYTE ENABLE, PATH 3 (D 31 D 24).                           |

| BE4#      | 0     | BYTE ENABLE, PATH4 (D39 D32).                              |

| BE5#      | 0     | BYTE ENABLE, PATH5 (D47:D40).                              |

| BE6#      | 0     | BYTE ENABLE, PATH6 (D55 D48).                              |

| BE7#      | 0     | byte enable , path7 (D63:D56).                             |

| SYMBOL    | TY PE | DESCRIPTION                                                    |

|-----------|-------|----------------------------------------------------------------|

| BF        | I     | THE BUS FREQUENCY SIGNAL (BF) DETE RM INES THE I/O BUS         |

|           |       | TO PROCESSOR CORE FREQUENCY RATID.                             |

| BOFF#     | I     | ENSURE THAT THE PROCESSOR DOESN T FETCH STALE DATA             |

|           |       | FROM MAIN MEMORY.                                              |

| BP3:2     | 0     | THE BREAK POINT OUTPUTS INDICATE THAT A BREAKPOINT             |

|           |       | M ATCH HAS BEEN DETECTED THROUGH THE BRESKPO NT                |

|           |       | REGISTER.                                                      |

| BP/PM 1:0 | 0     | BREAKPOINT AND PERFORMANCE MONIFORING PINS.                    |

| BRDY#     | I     | THE BURS READY INPUT INDICATES THAT THE CURRENTLY ADDRE-       |

|           |       | SSED DEVICE HAS PRESENTED VALID DATA ON THE DATA BUS PINS      |

|           |       | IN RESPONSE TO A READ OR THAT CURRENTLY ADDRESSED DEVICE       |

|           |       | HAS ACCEPTED DATA FROM THE PENTIUM CPU IN RESPONSE TO A        |

|           |       | W RITE.                                                        |

| BRDCY#    | I     | THE BURS READY INPUT INDICATES THAT THE LEVEL 2 CACHE HAS      |

|           |       | presented valid data on the data bus pins in response to $\mu$ |

|           |       | READ OR THAT THE LEVEL 2 CACHE HAS ACCEPTED DATA FROM          |

|           |       | THE PENTIUM CPU IN RESPONSE TO A WRITE.                        |

| BREQ#     | 0     | THE INTERNAL CYCLE PENDING OUTPUT INDICATES THAT THE           |

|           |       | PENTIUM MICROCESSOR HAS A BUS CYCLE REQUEST PENDING.           |

| вт3:Вт0   | NA    | BRANCH TRACE LINES ARE DRIVEN DURING A BRANCH TRACE            |

|           |       | SPEC AL CYCLE.                                                 |

| BUSCHK#   | I     | THE BUS CHECK ALLOW S SYSTEM DESIGNERS TO NOTIFY THE CPU       |

|           |       | IF A BUS CYCLE HAS NOT COM PLETED SUCCESSFULLY .               |

| CACHE#    | IO    | CACHE# SIGNAL IS ACTIVE W HEN INFORM ATION IS BEGIN            |

|           |       | TRANSFREED BETW EEN EXTERNAL M EM ORY AND AN INTERNAL          |

|           |       | CACHE.                                                         |

| CLK       | I     | CLOCK PROVIDES THE FUNDAM NTAL TIM ING AND THE INTERNAL        |

|           |       | OPERATING FREQUENCY FOR THEE PENTIUM M ICROPROCESSOR           |

| CPUTYP    | I     | CPU TYPE PIN SAM PLED BY THE PROCESSOR AT THE TRALING-         |

|           |       | EDGE OF RESET TO DETERM INE W HETHER IT IS PRIMARY OR THE      |

|           |       | DUAL PROCESSPR .                                               |

### 5.1 PENTIUM MICROPROCESSOR (P54LM)-2

| SYMBOL  | TYPE | DESCRIPTION                                               |

|---------|------|-----------------------------------------------------------|

| D7:D0   | I/O  | DATA PATH ZERO.                                           |

| D51:D8  | I/O  | DATA PATH ONE.                                            |

| D23:D16 | I/O  | DATA PATH TWO.                                            |

| D31:D24 | I/O  | DATA PATH THREE.                                          |

| D39:D32 | I/O  | DATA PATH FOUR.                                           |

| D47:D40 | I/O  | DATA PATH FIVE.                                           |

| D55:D48 | I/O  | DATA PATH SIX.                                            |

| D63:D56 | I/O  | DATA PATH SEVEN.                                          |

| D/C#    | I/O  | DATA OR CONTROL. AT THE START OF BUS CYCLE, THE PENTIUM   |

|         |      | PROCESSOR SETS THIS LINE HIGH IF DATA WILL BE TRANSFERED  |

| -       |      | DURING THE CURRENT BUS CYCLE, OTHERWISE SETS IT TO LOW.   |

| D/P#    | 0    | DUAL/PRIMARY.THIS IS AN OUTPUT OF PRIMARY PROCESSOR AND   |

|         |      | IS NOT USED BY THE DUAL PROCESSOR.IT ASSERTED(LOW) BY THE |

|         |      | PRIMARY PROCESSOR WHEN IT HAS ACQUIRED PRIVATE BUS OWN-   |

|         |      | ERSHIP AND HAS INITIATED A BUS CYCLE                      |

| DPO     | I/O  | PARITY BIT FOR DATA PATH 0,D7:D0.                         |

| DP1     | I/O  | PARITY BIT FOR DATA PATH 1,D15:D8.                        |

| DP2     | I/O  | PARITY BIT FOR DATA PATH 2,D23:D16.                       |

| DP3     | I/O  | PARITY BIT FOR DATA PATH 3,D31:D24.                       |

| DP4     | I/O  | PARITY BIT FOR DATA PATH 4,D39:D32.                       |

| DP5     | I/O  | PARITY BIT FOR DATA PATH 5,D47:D40.                       |

| DP6     | I/O  | PARITY BIT FOR DATA PATH 6,D55:D48.                       |

| DP7     | I/O  | PARITY BIT FOR DATA PATH 7,D63:D56.                       |

| DPEN#   | I/O  | DUAL PROCESSOR ENABLE.                                    |

| EADS#   | Ι    | THE EXTERNAL ADDRESS STROBE SIGNAL INDICATES THAT A VALID |

|         |      | EXTERNAL ADDRESS HAS BEEN DRIVEN ONTO THE PENTIUM'S A4:A3 |

|         |      | ADDRESS LINES BY ANOTHER MASTER.                          |

| EWBE#   | Ι    | THE EXTERNAL WRITE BUFFER EMPTY IS USED TO ENSURE THAT    |

|         |      | MEMORY OPERATIONS OCCUR IN ORDER OF EXECUTION.            |

| FLUSH#  | Ι    | THE CACHE FLUSH INPUT FORCES FORCES THE PENTIUM ROCE-     |

|         |      | SSOR TO FLUSH THE CONTENTS IN OF ITS INTERNAL CACHE.      |

| FERR#   | 0    | FLOATING0POINT ERROR OUTPUT PIN IS DRIVEN ACTIVE WHEN A   |

|         |      | FLOATING-POINT ERROR OCCURS.                              |

| SYMBOL | TYPE | DESCRIPTION                                               |

|--------|------|-----------------------------------------------------------|

| FRCMC# | I    | THE FUNCTOIN REDUNDANCY CHECKING MASTER/CHECKER# PIN IS   |

|        |      | SAMPLED BY THE PENTIUM MICROPROCESSOR DURING RESET TO     |

|        |      | DETERMINE WHETHER THE MICROPROCESSOR SHOULD BE CONFIG-    |

|        |      | ED AS A FUNCTIONAL REDUNDANCY MASTER OR CHECKER.          |

| HIT#   | I/O  | THE HIT# SIGNAL ACTIVE TO INDICATE A SNOOP HIT IN EITHER  |

|        |      | THE INTERNAL CODE OR DATA CACHE.                          |

| HITM#  | I/O  | THE PENTIUM MICOPROCESSOR DRIVES THE HIT MODIFIED         |

|        |      | SIGNAL ACTIVE TO INDICATE A SNOOP HIT TO A MODIFIED       |

|        |      | LINE IN THE DATA CACHE.                                   |

| HLDA   | I/O  | BUS HOLD ACKNOWLEDGE.                                     |

| HOLD   | I    | THE BUS HOLD REQUEST INPUT ALLOWS ANOTHER BUS MASTER      |

|        |      | TO GAIN COMPLETE CONTROL OF THE PENTIUM'S LOCAL BUSES.    |

| IBT    | NA   | THE INSTRUCTION BRANCH TAKEN SIGNAL IS DRIVEN ACTIVE FOR  |

|        |      | ONE CLOCK CYCLE WHEN PENTIUM MICROPROCESSOE EXECUTES      |

|        |      | AN INSTRUCTION RESULTING IN AN EXECUTION BRANCH.          |

| IERR#  | 0    | INTERNAL ERROR IS ASSERTED WHEN A PARITY ERROR IS ENCOU-  |

|        |      | NTERED INSIDE THE PENTIUM MICROPROCESSOR.                 |

| IGNNE# | I    | IGNORE NUMERIC ERROR INPUT IS ASSERTED BY EXTERNAL LOGIC  |

|        |      | THE PENTIUM MICROPROCESSOR WILL IGNORE A NUMERIC ERROR.   |

|        |      | AND CONTINUE EXECUTING NON-CONTROL FLOATING-POINT INSTRU- |

|        |      | CTIONS.                                                   |

| INIT   | I    | PENTIUM MICROCESSOR INIT INPUT HASTHE SAME EFFECT AS      |

|        |      | THE RESET SIGNAL EXCEPT THAT THE FOLLOWING RETAIN         |

|        |      | THE VALUES.                                               |

| INTR   | I    | THIS IS MASKABLE INTERRUPT REQUEST INPUT.                 |

| INV    | I    | THE INVALIDATE INPUT TELLS THE PENTIUM MICROPROCESSOR     |

|        |      | WHETHER THE CACHE LINE STATE SHOULD BE MARKED INVALIDAT-  |

|        |      | ED OR SHARED AS A RESULT OF SNOOP HIT.                    |

| IU     | NA   | THE IU SIGNAL IDICATED THAT AN INSTRUCTION IN THE "u"     |

|        |      | PIPLINE HAS COMPLETED EXECUTION.                          |

| IV     | NA   | THE IU SIGNAL IDICATED THAT AN INSTRUCTION IN THE "v"     |

|        |      | PIPLINE HAS COMPLETED EXECUTION.                          |

### 5.1 PENTIUM MICROPROCESSOR (P54LM)-3

| SYMBOL   | TYPE | DESCRIPTION                                                 |

|----------|------|-------------------------------------------------------------|

| KEN#     | Ι    | THE CACHE ENABLE PIN IS SAMPLED TO DETERMINE IF THE         |

|          |      | CURRENT BUS CYCLE IS CACHEABLE.                             |

| LINT0 OR | Ι    | IF THE PROCESSOR'S LOCAL APIC IS ENABLE, THIS IS THE        |

| INTR     |      | LINTO INPUT TO THE APIC.                                    |

| LOCK#    | I/O  | THE LOCK# SIGNAL IS ASSERTED WHEN THE PENTIUM               |

|          |      | MICROPROCESSOR WANTS TO RUN MULTIP BUS CYCLES               |

|          |      | WITHOUT HAVING THE BUSES TAKEN AWAY BY ANOTHER BUS          |

|          |      | MASTER.                                                     |

| M/IO#    | I/O  | MEMORY OR I/O. AT THE START OF BUS CYCLE, THE PENTIUM       |

|          |      | PROCESSOR SETS THIS LINE HIGH IF ADDRESSING A MEMORY LOC-   |

|          |      | ATION AND LOW IF ADDRESSING AN I/O LOCATION.                |

| NA#      | Ι    | THE NEXT ADDRESS INPUT INDICATES THAT THE MEMORY            |

|          |      | SUBSYSTEM IS CAPABLE FO TAKING ADVANTAGE OF THE             |

|          |      | PENTIUM MICROPROCESSOR'S ADDRESS PIPELINING.                |

| NMI      | Ι    | NON-MASKABLE INTERRUPT REQUEST.                             |

| PBREQ#   | I/O  | PRIVATE BUS REQUEST.ONLY USED IN DUAL PROCESSOR SYSTEM.     |

| PBGNT#   | I/O  | PRIVATE BUS GRANT.ONLY USED IN DUAL PROCESSOR SYSTEM.       |

| PCHK#    | 0    | SEE DP0.                                                    |

| PCD      | 0    | PAGE CACHE DISABLE.                                         |

| PEN#     | Ι    | PARITY ENABLE.                                              |

| PHIT#    | I/O  | PARIVATE BUS HIT.PHIT# IS AN OUTPUT FROM THE LRM AND AN     |

|          |      | INPUT TO THE MRM.TI IS USED IN A DUAL PROCESSOR SYTEM.      |

| PHITM#   | I/O  | PRIVATE BUS HIT ON MODIFIED LINE.                           |

| PICCLK   | Ι    | PROGRAMMABLE INTERRUPT CONTROLLER CLOCK.                    |

| PICDO OR | I/O  | PROGRAMMABLE INTERRUPT CONTROLLER DATA LINE0.               |

| DEPN#    |      |                                                             |

| PICD1 OR | I/O  | PROGRAMMABLE INTERRUPT CONTROLLER DATA LINE1.               |

| APICEN   |      |                                                             |

| PRDY     | 0    | PROBE READY.ASSERTED BY THE PROCESSOR WHEN IT HAS STOP-     |

|          |      | PED EXECUTION IN RESPONSE TO THE R/S# SIGNAL BEING ASSERTED |

|          |      | LOW.                                                        |

| PWT      | 0    | THE PAGE WRITE-THROUGHT PIN REFLECTS THE STATE OF THE       |

|          |      | PAGE ATTRIBUTE BIT.                                         |

| SYMBOL  | TYPE | DESCRIPTION                                                 |

|---------|------|-------------------------------------------------------------|

| RESET   | Ι    | 1.KEEPS THE MICROPROCESSOR FROM OPERATING UNTIL THE         |

|         |      | POWER SUPPLY VOLTAGES HAVE COME UP AND STSBILIZED.          |

|         |      | 2.FORCES KNOWN DEFAULT VALUES INTO THE PENTIUM              |

|         |      | PROCESSOR REGISTER.                                         |

| R/S#    | Ι    | RUN/STOP. WHEN SET HIGH, THE PROCESSOR IS PERMITTED TO      |

|         |      | RUN NORMALLY.WHEN SET LOW, THE PROCESSOR CEASES TO          |

|         |      | EXECUTE INSTRUCTIONS AND ENTERS PROBE MODE.                 |

| SCYC    | I/O  | SPLIT CYCLE IS VALID FOR LOCKED BUS CYCLES OLY.SCYC IS      |

|         |      | ASSERTED WHEN A LOCKED TRANSFER RESULTS IN A MISALIGNED     |

|         |      | MWMORY ACCESS.                                              |

| SMI#    | Ι    | SYSTEM MANAGEMENT INTERRUPT INFORMS THE PROCESSOR           |

|         |      | THAT A SYSTEM MANAGEMENT INTERRUPT ROUTINE.RESIDING IN      |

|         |      | SYSTEM MANAGEMENT ADDRESS SPACE NEEDS TO BE PERFORMED.      |

| SMICAT# | 0    | SYSTEM MANAGEMENT INTERRUPT ACKNOWEDGW INFORMS EXTE-        |

|         |      | RNAL LOGIC THAT THE PROCESSOR IS IN SYSTEM MANAGEMENT       |

|         |      | MODE.                                                       |

| TCK     | Ι    | TEST CLOCK.USED TO CLOCK STATE INFORMATION AND DATA INTO    |

|         |      | AND OUT OF DEVICE DURING BOUNDARY SCAN.                     |

| TDI     | Ι    | TEST INPUT.USED TO SHIFT DATA AND INSTRUCTIONS INTO THE     |

|         |      | TEST ACCESS PORT IN A SERIAL BIT STREAM.                    |

| TDO     | 0    | TEST OUTPUT.USED TO SHIFT DATA OUT OF THE TEST ACCESS PORT  |

|         |      | IN A SERIAL BIT STREAM.                                     |

| TMS     | Ι    | TEST MODE SELECT.USED TO CONTROL THE STATE OF THE TEST      |

|         |      | ACCESS PORT CONTROLLER.                                     |

| TRST#   | Ι    | TEST RESET.USED TO FORCE THE TEST ACCESS PORT CONTROLLER    |

|         |      | INTO AN INITIALIZED STATE.                                  |

| WB/WT#  | Ι    | THE WRITE-BACK OR WRITE THROUGH INPUT ALLOWS EXTERNAL       |

|         |      | LOGIC TO DETERMINE WHETHER A IS PLACED IN THE WRITE BACK    |

|         |      | OR WRITE THROUGH STATE.                                     |

| W/R#    | I/O  | WRITE OR READ.AT THE START OF A BUS CYCLE, THE PENTIUM      |

|         |      | PROCESSOR SETS THIS LINE HIGH IF THE CURRENT BUS CYCLE IS A |

|         |      | WRITE BUS CYCLE.W/R# IS SET LOW IF THE CURRENT BUS CYCLE    |

|         |      | IS A READ BUS CYCLE.                                        |

| Symbol            | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A20M#             | Ι    | When the <b>address bit 20 mask</b> pin is asserted, the Pentium ?processor with MMX <sub>TM</sub> technology emulates the address wraparound at 1 Mbyte which occurs on the 8086 by masking physical address bit 20 (A20) before performing a lookup to the internal caches or driving a memory cycle on the bus. The effect of A20M# is undefined in protected mode. A20M# must be asserted only when the processor is in real mode.<br>A20M# is internally masked by the Pentium processor with MMX technology when configured as a Dual processor. |

| A31-A3            | I/O  | As outputs, the <b>address</b> lines of the processor along with the byte enables define the physical area of memory or I/O accessed. The external system drives the inquire address to the processor on A31-A5.                                                                                                                                                                                                                                                                                                                                       |

| ADS#              | 0    | The <b>address strobe</b> indicates that a new valid bus cycle is currently being driven<br>by the Pentium processor with MMX technology.                                                                                                                                                                                                                                                                                                                                                                                                              |

| ADSC#             | 0    | The <b>address strobe (copy)</b> is functionally identical to ADS#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AHOLD             | Ι    | In response to the assertion of <b>address hold</b> , the Pentium processor with MMX technology will stop driving the address lines (A31-A3) and AP in the next clock. The rest of the bus will remain active so data can be returned or driven for previously issued bus cycles.                                                                                                                                                                                                                                                                      |

| АР                | I/O  | Address parity is driven by the Pentium processor with MMX technology with<br>even parity information on all Pentium processor with MMX technology generated<br>cycles in the same clock that the address is driven. Even parity must be driven<br>back to the Pentium processor with MMX technology during inquire cycles on this<br>pin in the same clock as EADS# to ensure that correct parity check status is<br>indicated by the Pentium processor with MMX technology.                                                                          |

| APCHK#            | 0    | The <b>address parity check</b> status pin is asserted two clocks after EADS# is sampled active if the Pentium processor with MMX technology has detected a parity error on the address bus during inquire cycles. APCHK# will remain active for one clock each time a parity error is detected (including during dual processing private snooping).                                                                                                                                                                                                   |

| [APICEN]<br>PICD1 | Ι    | Advanced Programmable Interrupt Controller Enable enables or disables the on-chip APIC interrupt controller. If sampled high at the falling edge of RESET, the APIC is enabled. APICEN shares a pin with the PICD1 signal.                                                                                                                                                                                                                                                                                                                             |

| Symbol                | Туре     | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BE7#-E4#<br>BE3#-E0#  | O<br>I/O | The <b>byte enable</b> pins are used to determine which bytes must be written to external memory or which bytes were requested by the CPU for the current cycle. The byte enables are driven in the same clock as the address lines (A31-3). Additionally, the lower 4-byte enables (BE3#-BE0#) are used on the Pentium processor with MMX technology as APIC ID inputs and are sampled at RESET. In dual processing mode, BE4# is used as an input during Flush cycles. |

| BF[1:0]               | Ι        | The <b>bus frequency</b> pins determine the bus-to-core frequency ratio. BF[1:0] are sampled at RESET, and cannot be changed until another non-warm (1 ms) assertion of RESET. Additionally, BF[1:0] must not change values while RESET is active. See Table 3 for Bus Frequency Selections.                                                                                                                                                                             |

| BOFF#                 | Ι        | The <b>backoff</b> input is used to abort all outstanding bus cycles that have not yet completed. In response to BOFF#, the Pentium processor with MMX technology will float all pins normally floated during bus hold in the next clock. The processor remains in bus hold until BOFF# is negated, at which time the Pentium processor with MMX technology restarts the aborted bus cycle(s) in their entirety.                                                         |

| BP[3:2]<br>PM/BP[1:0] | 0        | The <b>breakpoint</b> pins (BP3-0) correspond to the debug registers, DR3-DR0<br>These pins externally indicate a breakpoint match when the debug registers are<br>programmed to test for breakpoint matches.                                                                                                                                                                                                                                                            |

|                       |          | BP1 and BP0 are multiplexed with the <b>performance monitoring</b> pins (PM1 and PM0). The PB1 and PB0 bits in the Debug Mode Control Register determine if the pins are configured as breakpoint or performance monitoring pins. The pins come out of RESET configured for performance monitoring.                                                                                                                                                                      |

| BRDY#                 | Ι        | The <b>burst ready</b> input indicates that the external system has presented valid data<br>on the data pins in response to a read or that the external system has accepted<br>the Pentium processor with MMX technology data in response to a write request.<br>This signal is sampled in the T2, T12 and T2P bus states.                                                                                                                                               |

| BRDYC#                | Ι        | The <b>burst ready (copy)</b> is functionally identical to BRDY#.                                                                                                                                                                                                                                                                                                                                                                                                        |

| BREQ                  | 0        | The <b>bus request</b> output indicates to the external system that the Pentium processor with MMX technology has internally generated a bus request. This signal is always driven whether or not the Pentium processor with MMX technology is driving its bus.                                                                                                                                                                                                          |

| Symbol  | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUSCHK# | Ι    | The <b>bus check</b> input allows the system to signal an unsuccessful completion of a bus cycle. If this pin is sampled active, the Pentium processor with MMX technology will latch the address and control signals in the machine check registers. If, in addition, the MCE bit in CR4 is set, the Pentium processor with MMX technology will vector to the machine check exception.<br><b>NOTE:</b><br>To assure that BUSCHK# will always be recognized, STPCLK# must be deasserted any time BUSCHK# is asserted by the system, before the system allows another external bus cycle. If BUSCHK# is asserted by the system for a snoop cycle while STPCLK# remains asserted, usually (if MCE=1) the processor will vector to the exception after STPCLK# is deasserted. But if another snoop to the same line occurs during STPCLK# assertion, the processor can lose the BUSCHK# request. |

| CACHE#  | 0    | For Pentium processor with MMX technology-initiated cycles the <b>cache</b> pin<br>indicates internal cacheability of the cycle (if a read), and indicates a burst write<br>back cycle (if a write). If this pin is driven inactive during a read cycle, the Pentium<br>processor with MMX technology will not cache the returned data, regardless of the<br>state of the KEN# pin. This pin is also used to determine the cycle length (number<br>of transfers in the cycle).                                                                                                                                                                                                                                                                                                                                                                                                                |

| CLK     | Ι    | The <b>clock</b> input provides the fundamental timing for the Pentium processor with MMX technology. Its frequency is the operating frequency of the Pentium processor with MMX technology external bus, and requires TTL levels. All external timing parameters except TDI, TDO, TMS, TRST#, and PICD0-1 are specified with respect to the rising edge of CLK.<br>This pin is 3.3V-tolerant-only on the Pentium processor with MMX technology.<br>Please refer to the Pentium ?Processor Family Developer• Manual (Order Number 241428) for the CLK and PICCLK signal quality specification.<br><b>NOTE:</b><br>It is recommended that CLK begin toggling within 150 ms after VCC reaches its proper operating level. This recommendation is to ensure long-term reliability of the device.                                                                                                 |

| СРИТҮР  | I    | <b>CPU type</b> distinguishes the Primary processor from the Dual processor. In a single processor environment, or when the Pentium processor with MMX technology is acting as the Primary processor in a dual processing system, CPUTYP should be strapped to VSS. The Dual processor should have CPUTYP strapped to VCC3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D/C#    | 0    | The <b>data/code</b> output is one of the primary bus cycle definition pins. It is driven valid in the same clock as the ADS# signal is asserted. D/C# distinguishes between data and code or special cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Symbol           | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D/P#             | 0    | The <b>dual/primary</b> processor indication. The Primary processor drives this pin low<br>when it is driving the bus, otherwise it drives this pin high. D/P# is always driven.<br>D/P# can be sampled for the current cycle with ADS# (like a status pin). This pin<br>is defined only on the Primary processor. Dual processing is supported in a<br>system only if both processors are operating at identical core and bus<br>frequencies. Within these restrictions, two processors of different steppings may<br>operate together in a system. |

| D63-D0           | I/O  | These are the 64 <b>data lines</b> for the processor. Lines D7-D0 define the least significant byte of the data bus; lines D63-D56 define the most significant byte of the data bus. When the CPU is driving the data lines, they are driven during the T2, T12, or T2P clocks for that cycle. During reads, the CPU samples the data bus when BRDY# is returned.                                                                                                                                                                                    |

| DP7-DP0          | I/O  | These are the <b>data parity</b> pins for the processor. There is one for each byte of the data bus. They are driven by the Pentium processor with MMX technology with even parity information on writes in the same clock as write data. Even parity information must be driven back to the Pentium processor with MMX technology on these pins in the same clock as the data to ensure that the correct parity check status is indicated by the Pentium processor with MMX technology. DP7 applies to D63-56, DP0 applies to D7-0.                 |

| [DPEN#]<br>PICD0 | I/O  | <b>Dual processing enable</b> is an output of the Dual processor and an input of the Primary processor. The Dual processor drives DPEN# low to the Primary processor at RESET to indicate that the Primary processor should enable dual processor mode. DPEN# may be sampled by the system at the falling edge of RESET to determine if the dual-processor socket is occupied. DPEN# is multiplexed with PICD0.                                                                                                                                      |

| EADS#            | Ι    | This signal indicates that a valid <b>external address</b> has been driven onto the Pentium processor with MMX technology address pins to be used for an inquire cycle.                                                                                                                                                                                                                                                                                                                                                                              |

| EWBE#            | Ι    | The <b>external write buffer empty</b> input, when inactive (high), indicates that a write cycle is pending in the external system. When the Pentium processor with MMX technology generates a write, and EWBE# is sampled inactive, the Pentium processor with MMX technology will hold off all subsequent writes to all E- or M-state lines in the data cache until all write cycles have completed, as indicated by EWBE# being active.                                                                                                           |

| FERR#            | 0    | The <b>floating-point error</b> pin is driven active when an unmasked <b>floating-point</b><br>error occurs. FERR# is similar to the ERROR# pin on the Intel387?math<br>coprocessor. FERR# is included for compatibility with systems using DOS type<br><b>floating-point</b> error reporting. FERR# is never driven active by the Dual<br>processor. 12                                                                                                                                                                                             |

| Symbol | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLUSH# | Ι    | When asserted, the <b>cache flush</b> input forces the Pentium processor with MMX technology to write back all modified lines in the data cache and invalidate its internal caches. A Flush Acknowledge special cycle will be generated by the Pentium processor with MMX technology indicating completion of the write back and invalidation.<br>If FLUSH# is sampled low when RESET transitions from high to low, tristate test mode is entered.<br>If two Pentium processors with MMX technology are operating in dual processing mode and FLUSH# is asserted, the Dual processor will perform a flush first (without a flush acknowledge cycle), then the Primary processor will perform a flush followed by a flush acknowledge cycle.<br><b>NOTE:</b><br>If the FLUSH# signal is asserted in dual processing mode, it must be deasserted at least one clock prior to BRDY# of the FLUSH Acknowledge cycle to avoid DP arbitration problems. |

| FRCMC# | Ι    | Functional Redundancy Checking is not supported on the Pentium processor with MMX technology. The FRCMC# pin is not defined for the Pentium processor with MMX technology. This pin should be left as a • C?or tied to VCC3 via an external pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| HIT#   | 0    | The <b>hit</b> indication is driven to reflect the outcome of an inquire cycle. If an inquire cycle hits a valid line in either the Pentium processor with MMX technology data or instruction cache, this pin is asserted two clocks after EADS# is sampled asserted. If the inquire cycle misses the Pentium processor with MMX technology cache, this pin is negated two clocks after EADS#. This pin changes its value only as a result of an inquire cycle and retains its value between the cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| HITM#  | 0    | The <b>hit to a modified line</b> output is driven to reflect the outcome of an inquire cycle. It is asserted after inquire cycles which resulted in a hit to a modified line in the data cache. It is used to inhibit another bus master from accessing the data until the line is completely written back.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| HLDA   | 0    | The <b>bus hold acknowledge</b> pin goes active in response to a hold request driven<br>to the processor on the HOLD pin. It indicates that the Pentium processor with<br>MMX technology has floated most of the output pins and relinquished the bus to<br>another local bus master. When leaving bus hold, HLDA will be driven inactive<br>and the Pentium processor with MMX technology will resume driving the bus. If<br>the Pentium processor with MMX technology has a bus cycle pending, it will be<br>driven one clock cycle after HLDA is de-asserted.                                                                                                                                                                                                                                                                                                                                                                                  |

| Symbol     | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HOLD       | I    | In response to the <b>bus hold request</b> , the Pentium processor with MMX technology will float most of its output and input/output pins and assert HLDA after completing all outstanding bus cycles. The Pentium processor with MMX technology will maintain its bus in this state until HOLD is de-asserted. HOLD is not recognized during LOCK cycles. The Pentium processor with MMX technology will recognize HOLD during reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| IERR#      | 0    | The <b>internal error</b> pin is used to indicate internal parity errors. If a parity error occurs on a read from an internal array, the Pentium processor with MMX technology will assert the IERR# pin for one clock and then shutdown.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IGNNE#     | Ι    | This is the <b>ignore numeric error</b> input. This pin has no effect when the NE bit in CR0 is set to 1. When the CR0.NE bit is 0, and the IGNNE# pin is asserted, the Pentium processor with MMX technology will ignore any pending unmasked numeric exception and continue executing floating-point instructions for the entire duration that this pin is asserted. When the CR0.NE bit is 0, IGNNE# is not asserted, a pending unmasked numeric exception exists (SW.ES = 1), and the floating-point instruction is one of FINIT, FCLEX, FSTENV, FSAVE, FSTSW, FSTCW, FENI, FDISI, or FSETPM, the Pentium processor with MMX technology will execute the instruction in spite of the pending exception exists (SW.ES = 1), and the floating-point instruction in spite of the pending exception. When the CR0.NE bit is 0, IGNNE# is not asserted a pending unmasked numeric exception exists (SW.ES = 1), and the floating-point instruction is one other than FINIT, FCLEX, FSTENV, FSAVE, FSTENV, FSAVE, FSTSW, FSTCW, FENI, FDISI, or FSETPM, the Pentium processor with MMX technology will stop execution and wait for an external interrupt. IGNNE# is internally masked when the Pentium processor with MMX technology is configured as a Dual processor. |

| INIT       | Ι    | The Pentium processor with MMX technology <b>initialization</b> input pin forces the<br>Pentium processor with MMX technology to begin execution in a known state. The<br>processor state after INIT is the same as the state after RESET except that the<br>internal caches, write buffers, and floating-point registers retain the values they had<br>prior to INIT. INIT may NOT be used in lieu of RESET after power-up.<br>If INIT is sampled high when RESET transitions from high to low, the Pentium<br>processor with MMX technology will perform built-in self test prior to the start of<br>program execution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| INTR/LINT( | ) I  | An active <b>maskable interrupt</b> input indicates that an external interrupt has been generated. If the IF bit in the EFLAGS register is set, the Pentium processor with MMX technology will generate two locked interrupt acknowledge bus cycles and vector to an interrupt handler after the current instruction execution is completed. INTR must remain active until the first interrupt acknowledge cycle is generated to assure that the interrupt is recognized. If the local APIC is enabled, this pin becomes LINT0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Symbol     | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INV        | Ι    | The <b>invalidation</b> input determines the final cache line state (S or I) in case of an inquire cycle hit. It is sampled together with the address for the inquire cycle in the clock EADS# is sampled active.                                                                                                                                                                                                                                      |

| KEN#       | Ι    | The <b>cache enable</b> pin is used to determine whether the current cycle is cacheable or not and is consequently used to determine cycle length. When the Pentium processor with MMX technology generates a cycle that can be cached (CACHE# asserted) and KEN# is active, the cycle will be transformed into a burst line fill cycle.                                                                                                               |

| LINT0/INTF | LI   | If the APIC is enabled, this pin is <b>local interrupt 0</b> . If the APIC is disabled, this pin is INTR.                                                                                                                                                                                                                                                                                                                                              |

| LINT1/NMI  | Ι    | If the APIC is enabled, this pin is <b>local interrupt 1</b> . If the APIC is disabled, this pin is NMI.                                                                                                                                                                                                                                                                                                                                               |

| LOCK#      | 0    | The <b>bus lock</b> pin indicates that the current bus cycle is locked. The Pentium processor with MMX technology will not allow a bus hold when LOCK# is asserted (but AHOLD and BOFF# are allowed). LOCK# goes active in the first clock of the first locked bus cycle and goes inactive after the BRDY# is returned for the last locked bus cycle. LOCK# is guaranteed to be de-asserted for at least one clock between back-to-back locked cycles. |

| M/IO#      | 0    | The <b>memory/input-output</b> is one of the primary bus cycle definition pins. It is driven valid in the same clock as the ADS# signal is asserted. M/IO# distinguishes between memory and I/O cycles.                                                                                                                                                                                                                                                |

| NA#        | Ι    | An active <b>next address</b> input indicates that the external memory system is ready<br>to accept a new bus cycle although all data transfers for the current cycle have<br>not yet completed. The Pentium processor with MMX technology will issue ADS# for<br>a pending cycle two clocks after NA# is asserted. The Pentium processor with MMX<br>technology supports up to 2 outstanding bus cycles.                                              |

| NMI/LINT1  | Ι    | The <b>non-maskable interrupt</b> request signal indicates that an external non-maskable interrupt has been generated.<br>If the local APIC is enabled, this pin becomes LINT1.                                                                                                                                                                                                                                                                        |

| PBGNT#     | I/O  | <b>Private bus grant</b> is the grant line that is used when two Pentium processors with MMX technology are configured in dual processing mode, in order to perform private bus arbitration. PBGNT# should be left unconnected if only one Pentium processor with MMX technology exists in a system.                                                                                                                                                   |

| Symbol | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PBREQ# | I/O  | <b>Private bus request</b> is the request line that is used when two Pentium processor with MMX technology are configured in dual processing mode, in order to perform private bus arbitration. PBREQ# should be left unconnected if only one Pentium processor with MMX technology exists in a system.                                                                                                                                                                                                                                                                                                     |

| PCD    | 0    | The <b>page cache disable</b> pin reflects the state of the PCD bit in CR3, the Page Directory Entry, or the Page Table Entry. The purpose of PCD is to provide an external cacheability indication on a page by page basis.                                                                                                                                                                                                                                                                                                                                                                                |

| PCHK#  | 0    | The <b>parity check</b> output indicates the result of a parity check on a data read. It is<br>driven with parity status two clocks after BRDY# is returned. PCHK# remains low<br>one clock for each clock in which a parity error was detected. Parity is checked<br>only for the bytes on which valid data is returned.<br>When two Pentium processors with MMX technology are operating in dual<br>processing mode, PCHK# may be driven two or three clocks after BRDY# is<br>returned.                                                                                                                  |

| PEN#   | I    | The <b>parity enable</b> input (along with CR4.MCE) determines whether a machine check exception will be taken as a result of a data parity error on a read cycle. If this pin is sampled active in the clock a data parity error is detected, the Pentium processor with MMX technology will latch the address and control signals of the cycle with the parity error in the machine check registers. If, in addition, the machine check enable bit in CR4 is set to ?? the Pentium processor with MMX technology will vector to the machine check exception before the beginning of the next instruction. |

| PHIT#  | I/O  | <b>Private hit</b> is a hit indication used when two Pentium processors with MMX technology are configured in dual processing mode, in order to maintain local cache coherency. PHIT# should be left unconnected if only one Pentium processor with MMX technology exists in a system.                                                                                                                                                                                                                                                                                                                      |

| PHITM# | I/O  | <b>Private modified hit</b> is a hit on a modified cache line indication used when two<br>Pentium processors with MMX technology are configured in dual processing<br>mode, in order to maintain local cache coherency. PHITM# should be left<br>unconnected if only one Pentium processor with MMX technology exists in a<br>system.                                                                                                                                                                                                                                                                       |

| PICCLK | I    | The APIC interrupt controller serial data bus clock is driven into the <b>programmable interrupt controller clock</b> input of the Pentium processor with MMX technology.<br>This pin is 3.3V-tolerant-only on the Pentium processor with MMX technology.<br>Please refer to the Pentium ?Processor Family Developer• Manual (Order Number 241428) for the CLK and PICCLK signal quality specification.                                                                                                                                                                                                     |

| Symbol                         | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PICD0-1<br>[DPEN#]<br>[APICEN] | I/O  | <b>Programmable interrupt controller data lines 0-1</b> of the Pentium processor with MMX technology comprise the data portion of the APIC 3-wire bus. They are open-drain outputs that require external pull-up resistors. These signals are multiplexed with DPEN# and APICEN respectively.                                                                                                                                                    |

| PM/BP[1:0]                     | 0    | These pins function as part of the performance monitoring feature.<br>The breakpoint 1-0 pins are multiplexed with the <b>performance monitoring 1-0</b> pins. The PB1 and PB0 bits in the Debug Mode Control Register determine if the pins are configured as breakpoint or performance monitoring pins. The pins come out of RESET configured for performance monitoring.                                                                      |

| PRDY                           | 0    | The <b>probe ready</b> output pin is provided for use with the Intel debug port. Please refer to the Pentium?Processor Family Developer • Manual (Order Number 241428) for more details.                                                                                                                                                                                                                                                         |

| PWT                            | 0    | The <b>page write through</b> pin reflects the state of the PWT bit in CR3, the page directory entry, or the page table entry. The PWT pin is used to provide an external write back indication on a page-by-page basis.                                                                                                                                                                                                                         |

| R/S#                           | Ι    | The <b>run/stop</b> input is provided for use with the Intel debug port. Please refer to the Pentium?Processor Family Developer• Manual (Order Number 241428) for more details.                                                                                                                                                                                                                                                                  |

| RESET                          | Ι    | <b>RESET</b> forces the Pentium processor with MMX technology to begin execution at a known state. All the Pentium processor with MMX technology internal caches will be invalidated upon the RESET. Modified lines in the data cache are not written back. FLUSH# and INIT are sampled when RESET transitions from high to low to determine if tristate test mode or checker mode will be entered, or if Built-In Self-Test (BIST) will be run. |

| SCYC                           | 0    | The <b>split cycle</b> output is asserted during misaligned LOCKed transfers to indicate that more than two cycles will be locked together. This signal is defined for locked cycles only. It is undefined for cycles which are not locked.                                                                                                                                                                                                      |

| SMI#                           | Ι    | The <b>system management interrupt</b> causes a system management interrupt request to be latched internally. When the latched SMI# is recognized on an instruction boundary, the processor enters System Management Mode.                                                                                                                                                                                                                       |

| SMIACT#                        | 0    | An active <b>system management interrupt active</b> output indicates that the processor is operating in System Management Mode.                                                                                                                                                                                                                                                                                                                  |

| Symbol       | Туре   | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STPCLK#      | Ι      | Assertion of the <b>stop clock</b> input signifies a request to stop the internal clock of the Pentium processor with MMX technology, thereby causing the core to consume less power. When the CPU recognizes STPCLK#, the processor will stop execution on the next instruction boundary, unless superseded by a higher priority interrupt, and generate a stop grant acknowledge cycle. When STPCLK# is asserted, the Pentium processor with MMX technology will still respond to interprocessor and external snoop requests. |

| ТСК          | Ι      | The <b>testability clock</b> input provides the clocking function for the Pentium processor with MMX technology boundary scan in accordance with the IEEE Boundary Scan interface (Standard 1149.1). It is used to clock state information and data into and out of the Pentium processor with MMX technology during boundary scan.                                                                                                                                                                                             |

| TDI          | Ι      | The <b>test data input</b> is a serial input for the test logic. TAP instructions and data are shifted into the Pentium processor with MMX technology on the TDI pin on the rising edge of TCK when the TAP controller is in an appropriate state.                                                                                                                                                                                                                                                                              |

| TDO          | 0      | The <b>test data output</b> is a serial output of the test logic. TAP instructions and data are shifted out of the Pentium processor with MMX technology on the TDO pin on TCK 's falling edge when the TAP controller is in an appropriate state.                                                                                                                                                                                                                                                                              |

| TMS          | Ι      | The value of the <b>test mode select</b> input signal sampled at the rising edge of TCK controls the sequence of TAP controller state changes.                                                                                                                                                                                                                                                                                                                                                                                  |

| TRST#        | Ι      | When asserted, the <b>test reset</b> input allows the TAP controller to be asynchronously initialized.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VCC2<br>VCC3 | I<br>I | The Pentium processor with MMX technology has 25 2.8V <b>power</b> inputs.<br>The Pentium processor with MMX technology has 28 3.3V <b>power</b> inputs.                                                                                                                                                                                                                                                                                                                                                                        |

| VCC2DET#     | 0      | VCC2 detect is used in flexible motherboard implementations to configure the voltage output set-point appropriately for the VCC2 inputs of the processor.                                                                                                                                                                                                                                                                                                                                                                       |